CDCI6214

CDCI6214 is Ultra-Low Power Clock Generator manufactured by Texas Instruments.

Features

- One configurable high performance, low-power PLL with four programmable outputs

- RMS jitter performance

- Supports PCIe Gen1/ Gen2 / Gen3 / Gen4 without SSC

- Typical power consumption: 150m W at 1.8V(2)

- Universal clock input

- Differential AC-coupled or LVCMOS: 1MHz to 250MHz

- Crystal: 8MHz to 50MHz

- Flexible output frequencies

- 44.1k Hz to 350MHz

- Glitchless output divider switching

- Four individually configurable outputs

- LVCMOS, LVDS or HCSL

- Differential AC-coupled with programmable swing (LVDS-, CML-, LVPECL-patible)

- Fully integrated PLL, configurable loop bandwidth:

100k Hz to 3MHz

- Single or mixed supply operation for level translation: 1.8V, 2.5V and 3.3V

- Configurable GPIOs

- Status signals

- Up to four individual output enables

- Output divider synchronization

- Flexible configuration options

- I2C-patible interface: up to 400k Hz

- Integrated EEPROM with two pages and external select pin

- Only supports 100Ω systems

- Industrial temperature range:

- 40°C to 85°C

- Small footprint: 24-pin VQFN (4mm × 4mm)

2 Applications

- PCIe Gen 1/2/3/4 clocking

- 1G / 10G Ethernet switches, NIC, accelerators

- Test & measurement, handheld equipment

- Multi-function printers

- Broadcast infrastructure

3 Description

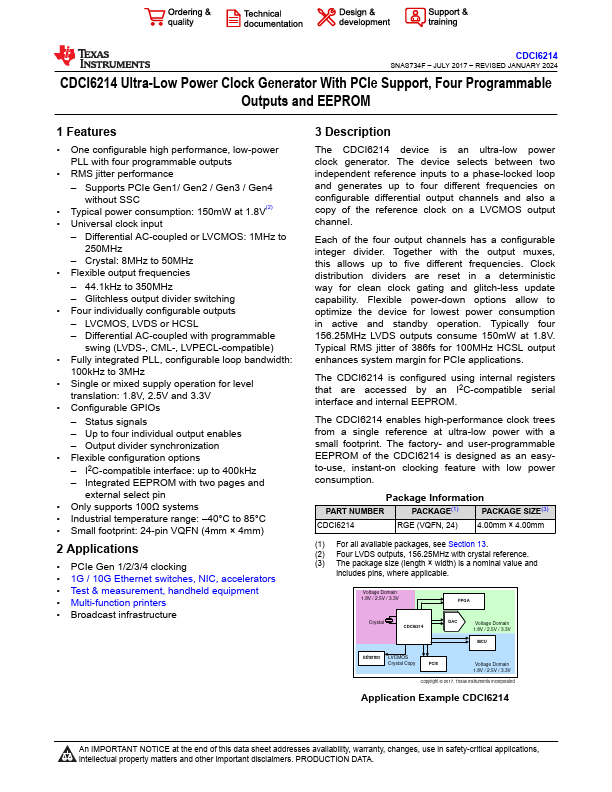

The CDCI6214 device is an ultra-low power clock generator. The device selects between two independent reference inputs to a phase-locked loop and generates up to four different frequencies on configurable differential output channels and also a copy of the reference clock on a LVCMOS output channel.

Each of the four output channels has a configurable integer divider. Together with the output muxes, this allows up to five different frequencies. Clock distribution dividers are reset in a deterministic way for clean clock gating and glitch-less update capability. Flexible power-down options allow to optimize the device for lowest power consumption in active and standby operation. Typically four 156.25MHz LVDS outputs consume 150m W at...