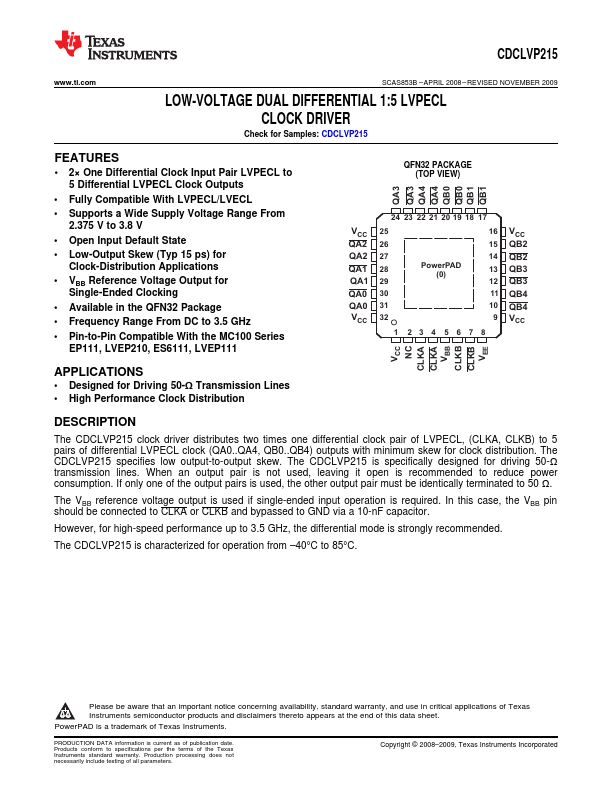

CDCLVP215 Description

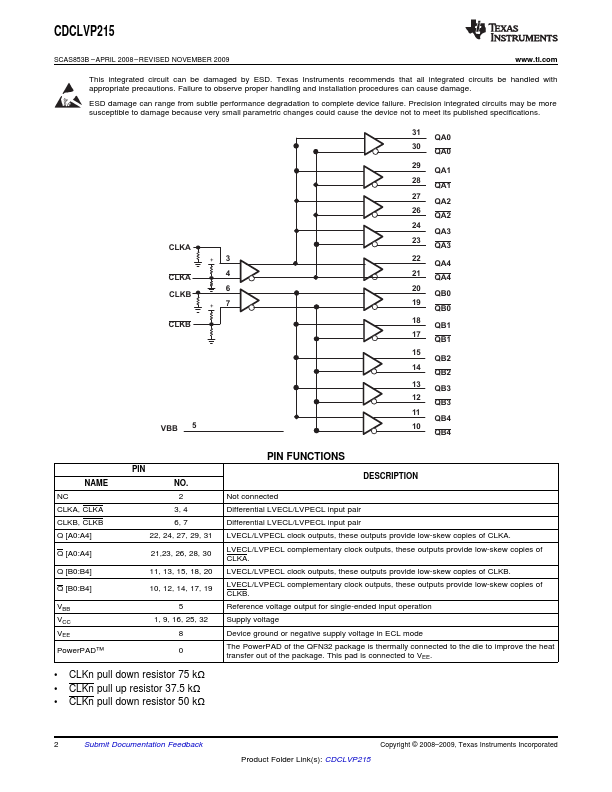

The CDCLVP215 clock driver distributes two times one differential clock pair of LVPECL, (CLKA, CLKB) to 5 pairs of differential LVPECL clock (QA0..QA4, QB0..QB4) outputs with minimum skew for clock distribution. The CDCLVP215 specifies low output-to-output skew. The CDCLVP215 is specifically designed for driving 50-Ω transmission lines.

CDCLVP215 Key Features

- 2 2× One Differential Clock Input Pair LVPECL to 5 Differential LVPECL Clock Outputs

- Fully patible With LVPECL/LVECL

- Supports a Wide Supply Voltage Range From

- Open Input Default State

CDCLVP215 Applications

- VBB Reference Voltage Output for