SN74ACT1071 Overview

Key Specifications

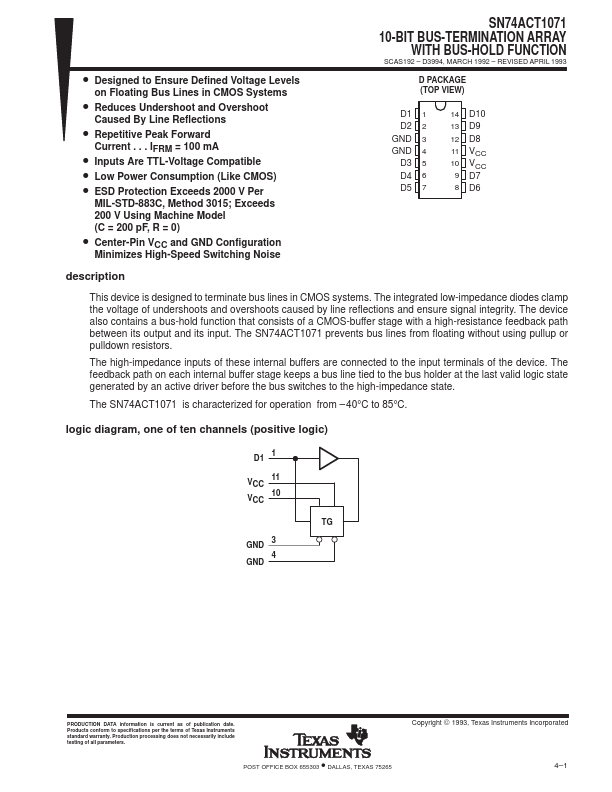

Package: SOIC

Mount Type: Surface Mount

Pins: 14

Operating Voltage: 5.5 V

Description

This device is designed to terminate bus lines in CMOS systems. The integrated low-impedance diodes clamp the voltage of undershoots and overshoots caused by line reflections and ensure signal integrity.