SN74ALS166 Overview

Key Specifications

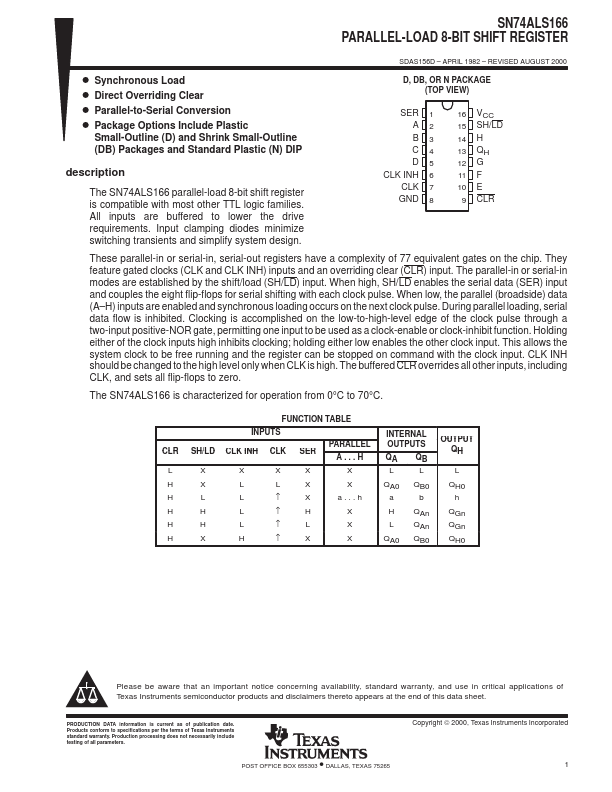

Package: PDIP

Mount Type: Through Hole

Pins: 16

Operating Voltage: 5 V

Description

The SN74ALS166 parallel-load 8-bit shift register is compatible with most other TTL logic families. All inputs are buffered to lower the drive requirements.

Key Features

- gated clocks (CLK and CLK INH) inputs and an overriding clear (CLR) input

- The parallel-in or serial-in modes are established by the shift/load (SH/LD) input

- When high, SH/LD enables the serial data (SER) input and couples the eight flip-flops for serial shifting with each clock pulse

- When low, the parallel (broadside) data (A–H) inputs are enabled and synchronous loading occurs on the next clock pulse

- During parallel loading, serial data flow is inhibited