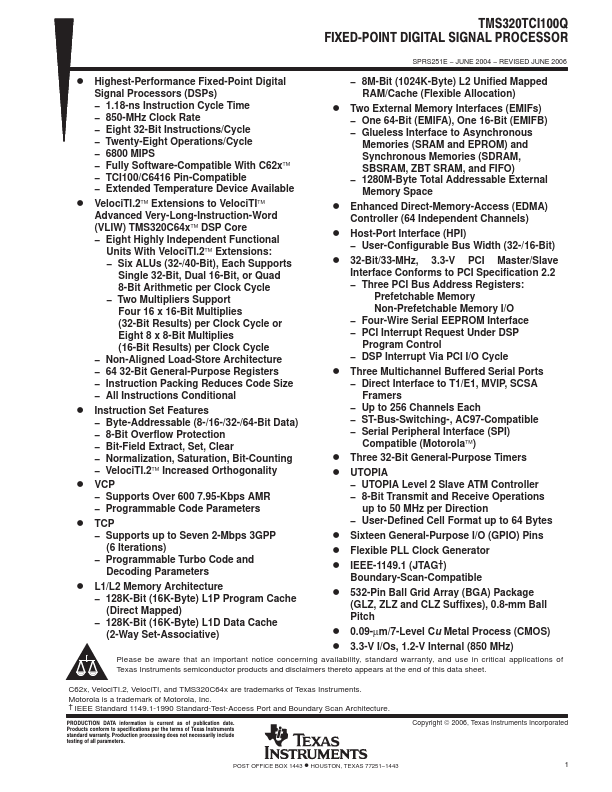

TMS320TCI100Q Overview

Prefetchable Memory Non-Prefetchable Memory I/O − Four-Wire Serial EEPROM Interface − PCI Interrupt Request Under DSP Program Control − DSP Interrupt Via PCI I/O Cycle D Three Multichannel Buffered Serial Ports − Instruction Packing Reduces Code Size − Direct Interface to T1/E1, MVIP, SCSA − All Instructions Conditional Framers D Instruction Set.

TMS320TCI100Q Key Features

- Byte-Addressable (8-/16-/32-/64-Bit Data)

- 8-Bit Overflow Protection

- Bit-Field Extract, Set, Clear

- Normalization, Saturation, Bit-Counting

- Up to 256 Channels Each

- ST-Bus-Switching-, AC97-patible

- Serial Peripheral Interface (SPI)

- VelociTI.2 Increased Orthogonality

- UTOPIA Level 2 Slave ATM Controller

- Supports Over 600 7.95-Kbps AMR