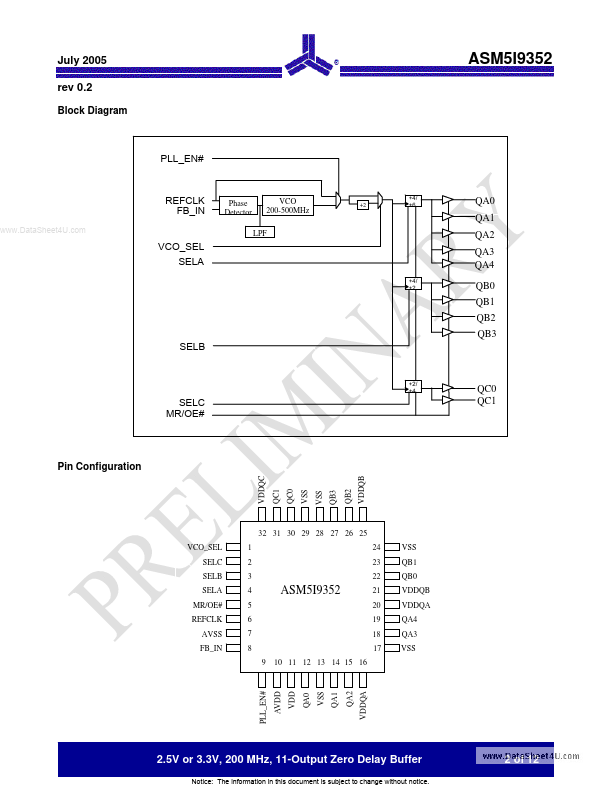

ASM5I9352 Key Features

- Output frequency range: 25MHz to 200MHz Output frequency range: 16.67MHz to 200MHz Input frequency range: 16.67MHz to 20

- 2.5V or 3.3V operation

- Split 2.5V/3.3V outputs ± 2% max Output duty cycle variation 11 Clock outputs: Drive up to 22 clock lines LVCMOS referen