CY2309

Overview

- 10 MHz to 100/133 MHz operating range, compatible with CPU and PCI bus frequencies

- Zero input-output propagation delay

- 60-ps typical cycle-to-cycle jitter (high drive)

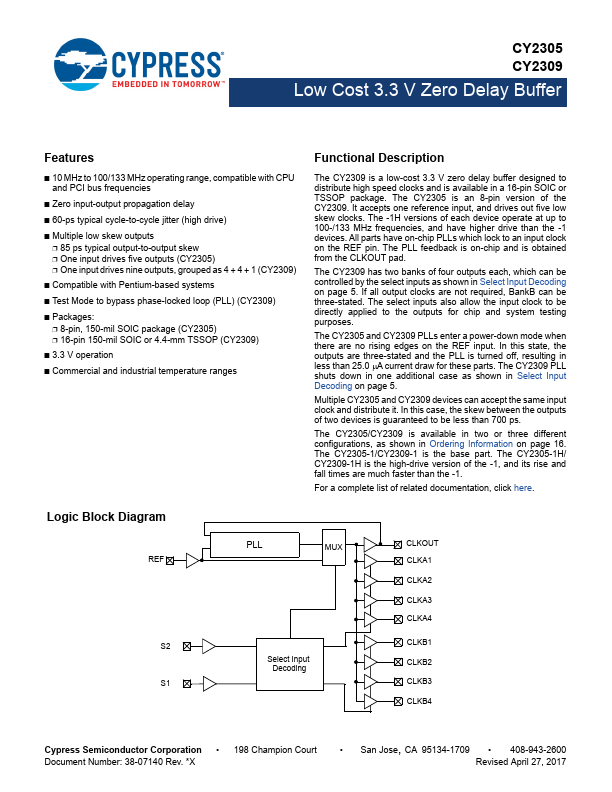

- Multiple low skew outputs ❐ 85 ps typical output-to-output skew ❐ One input drives five outputs (CY2305) ❐ One input drives nine outputs, grouped as 4 + 4 + 1 (CY2309)

- Compatible with Pentium-based systems

- Test Mode to bypass phase-locked loop (PLL) (CY2309)

- Packages: ❐ 8-pin, 150-mil SOIC package (CY2305) ❐ 16-pin 150-mil SOIC or 4.4-mm TSSOP (CY2309)

- 3.3 V operation

- Commercial and industrial temperature ranges Functional Description The CY2309 is a low-cost 3.3 V zero delay buffer designed to distribute high speed clocks and is available in a 16-pin SOIC or TSSOP package. The CY2305 is an 8-pin version of the CY2309. It accepts one reference input, and drives out five low skew clocks.