CY7C1360V25 Overview

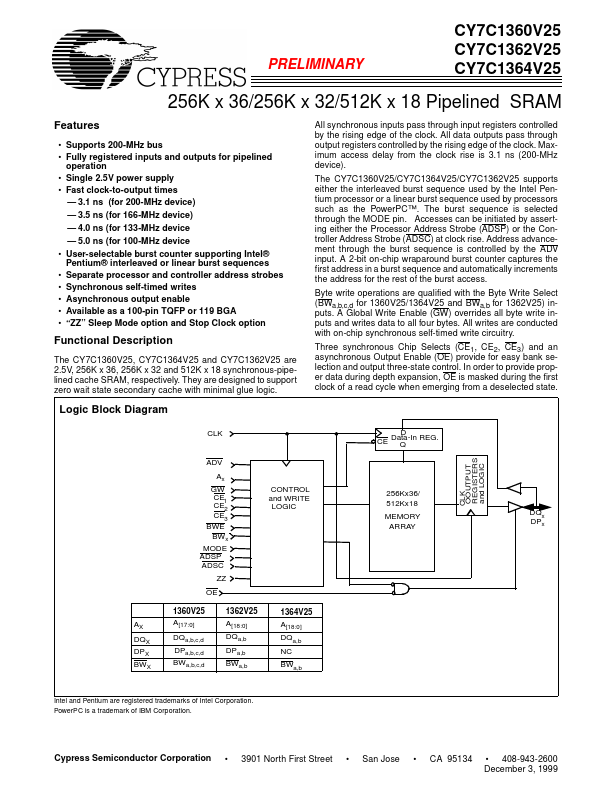

They are designed to support zero wait state secondary cache with minimal glue logic. Logic Block Diagram All synchronous inputs pass through.

CY7C1360V25 Key Features

- Supports 200-MHz bus

- Fully registered inputs and outputs for pipelined

- Single 2.5V power supply

- Fast clock-to-output times

- 3.1 ns (for 200-MHz device)

- 3.5 ns (for 166-MHz device)

- 4.0 ns (for 133-MHz device

- 5.0 ns (for 100-MHz device

- User-selectable burst counter supporting Intel® Pentium® interleaved or linear burst sequences

- Separate processor and controller address strobes