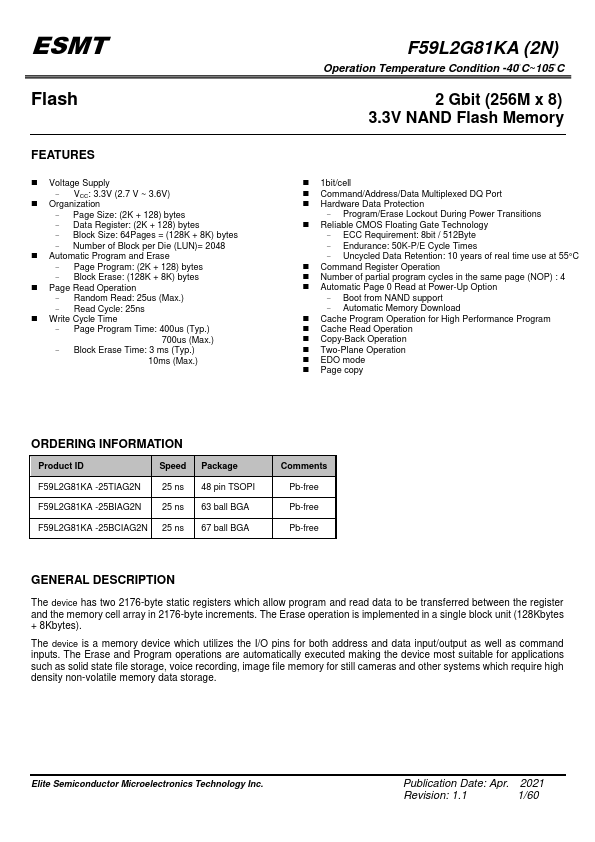

F59L2G81KA

F59L2G81KA is 2-Gbit 3.3V NAND Flash Memory manufactured by Elite Semiconductor Microelectronics Technology.

ESMT

Flash

Features

- Voltage Supply VCC: 3.3V (2.7 V ~ 3.6V)

- Organization Page Size: (2K + 128) bytes Data Register: (2K + 128) bytes Block Size: 64Pages = (128K + 8K) bytes Number of Block per Die (LUN)= 2048

- Automatic Program and Erase Page Program: (2K + 128) bytes Block Erase: (128K + 8K) bytes

- Page Read Operation Random Read: 25us (Max.) Read Cycle: 25ns

- Write Cycle Time Page Program Time: 400us (Typ.) 700us (Max.) Block Erase Time: 3 ms (Typ.) 10ms (Max.)

F59L2G81KA (2N)

Operation Temperature Condition -40°C~105°C

2 Gbit (256M x 8) 3.3V NAND Flash Memory

- 1bit/cell

- mand/Address/Data Multiplexed DQ Port

- Hardware Data Protection

Program/Erase...