74F114

Description

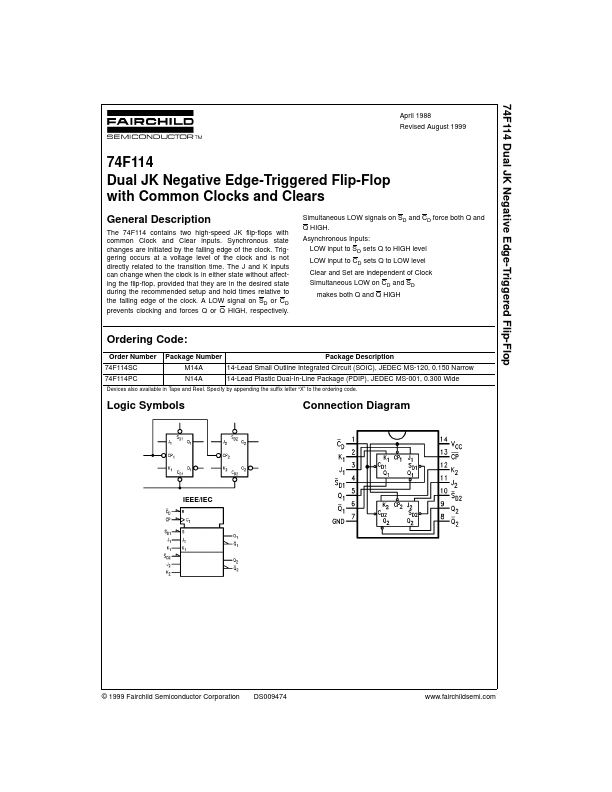

The 74F114 contains two high-speed JK flip-flops with mon Clock and Clear inputs. Synchronous state changes are initiated by the falling edge of the clock. Triggering occurs at a voltage level of the clock and is not directly related to the transition time. The J and K inputs can change when the clock is in either state without affecting the flip-flop, provided that they are in the desired state during the remended setup and hold times relative to the falling edge of the clock. A LOW signal on SD or CD prevents clocking and forces Q or Q HIGH, respectively. Simultaneous LOW signals on SD and CD force both Q and Q HIGH. Asynchronous Inputs: LOW input to SD sets Q to HIGH level LOW input to CD sets Q to LOW level Clear and Set are independent of Clock Simultaneous LOW on CD and SD makes both Q and Q HIGH

Ordering Code:

Order Number 74F114SC 74F114PC Package Number M14A N14A Package Description

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow...