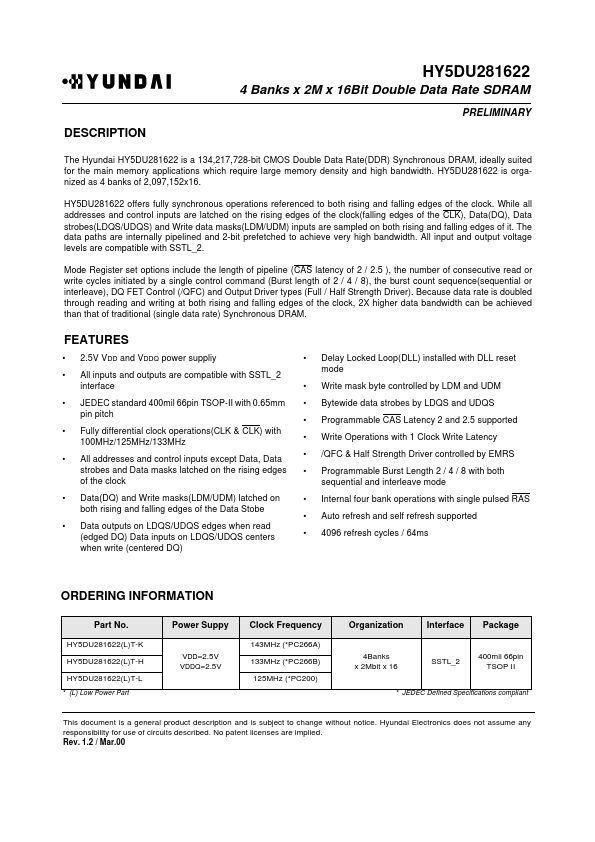

HY5DU281622T-L Key Features

- 2.5V V DD and VDDQ power suppliy All inputs and outputs are patible with SSTL_2 interface JEDEC standard 400mil 66pin TS

- Delay Locked Loop(DLL) installed with DLL reset mode Write mask byte controlled by LDM and UDM Bytewide data strobes by

- (L) Low Power Part

- JEDEC Defined Specifications pliant