854S057B

Description

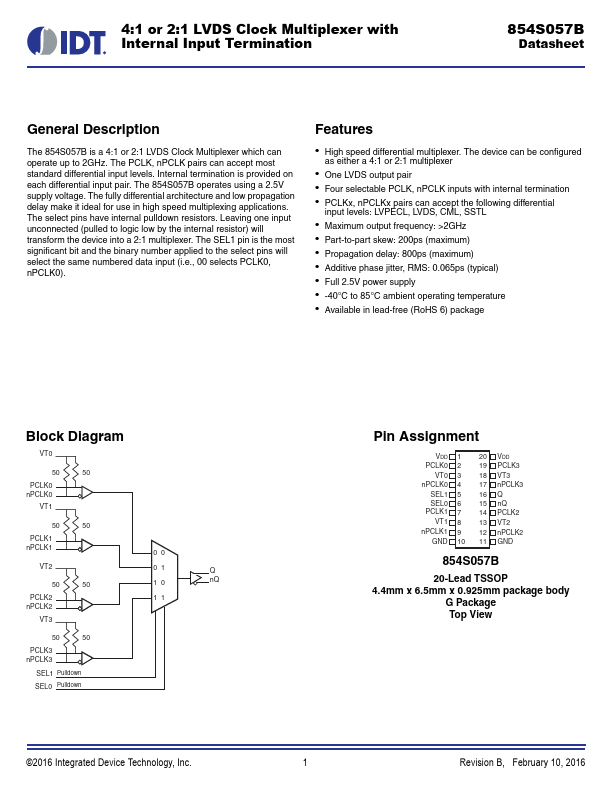

The 854S057B is a 4:1 or 2:1 LVDS Clock Multiplexer which can operate up to 2GHz. The PCLK, nPCLK pairs can accept most standard differential input levels.

Key Features

- High speed differential multiplexer. The device can be configured as either a 4:1 or 2:1 multiplexer

- One LVDS output pair

- Four sele