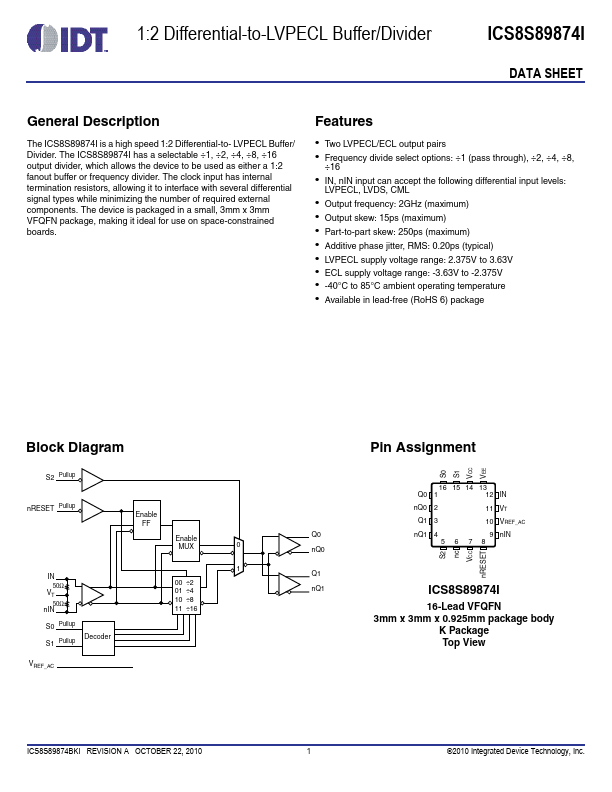

ICS8S89874I Description

The ICS8S89874I is a high speed 1:2 Differential-to- LVPECL Buffer/ Divider. The ICS8S89874I has a selectable ÷1, ÷2, ÷4, ÷8, ÷16 output divider, which allows the device to be used as either a 1:2 fanout buffer or frequency divider. The clock input has internal termination resistors, allowing it to interface with several differential signal types while minimizing the number of required external ponents.

ICS8S89874I Key Features

- Two LVPECL/ECL output pairs

- Frequency divide select options: ÷1 (pass through), ÷2, ÷4, ÷8

- IN, nIN input can accept the following differential input levels

- Output frequency: 2GHz (maximum)

- Output skew: 15ps (maximum)

- Part-to-part skew: 250ps (maximum)

- Additive phase jitter, RMS: 0.20ps (typical)

- LVPECL supply vol