ICS2510C Description

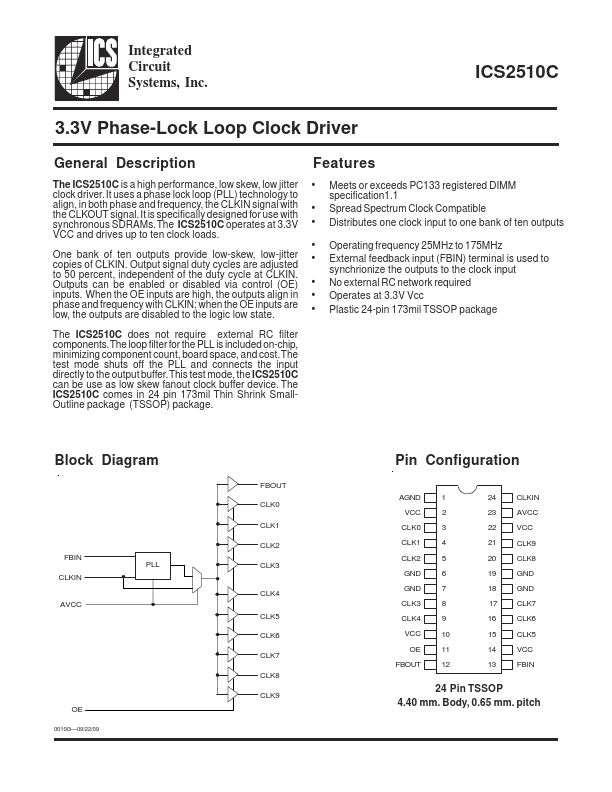

The ICS2510C is a high performance, low skew, low jitter clock driver. It uses a phase lock loop (PLL) technology to align, in both phase and frequency, the CLKIN signal with the CLKOUT signal. It is specifically designed for use with synchronous SDRAMs.

ICS2510C Key Features

- Meets or exceeds PC133 registered DIMM specification1.1 Spread Spectrum Clock patible Distributes one clock input to one