IDT23S05 Overview

Key Specifications

Package: SOP

Operating Voltage: 2.5 V

Max Voltage (typical range): 2.7 V

Min Voltage (typical range): 2.3 V

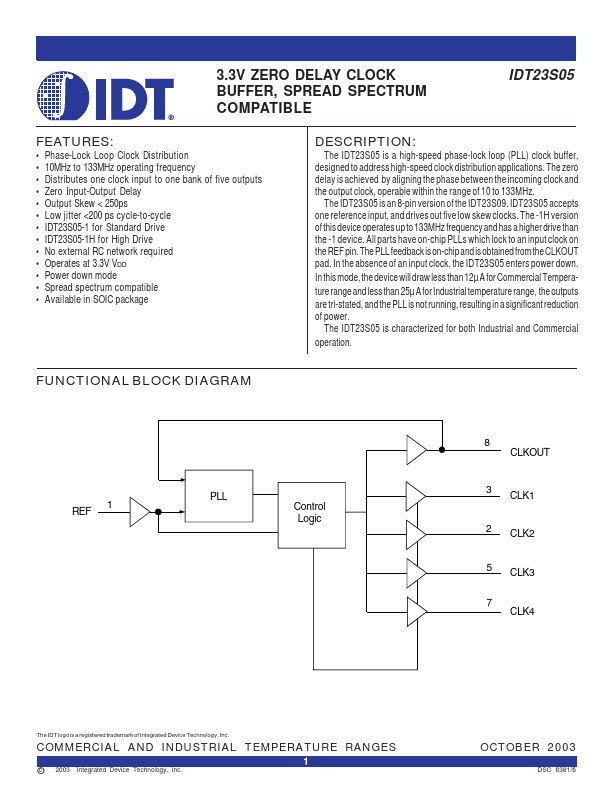

Description

The IDT23S05 is a high-speed phase-lock loop (PLL) clock buffer, designed to address high-speed clock distribution applications. The zero delay is achieved by aligning the phase between the incoming clock and the output clock, operable within the range of 10 to 133MHz.