IDT23S05T Overview

Key Specifications

Package: SOP

Mount Type: Surface Mount

Operating Voltage: 2.5 V

Max Voltage (typical range): 2.7 V

Description

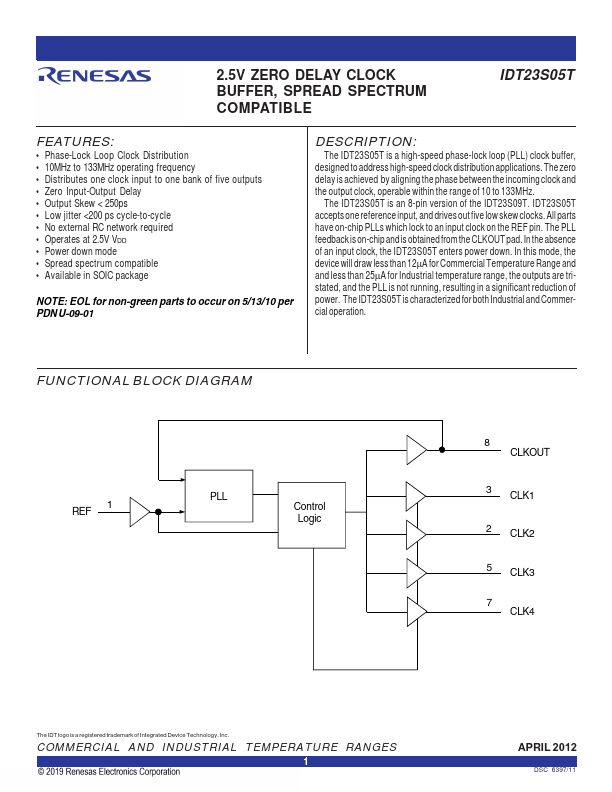

The IDT23S05T is a high-speed phase-lock loop (PLL) clock buffer, designed to address high-speed clock distribution applications. The zero delay is achieved by aligning the phase between the incoming clock and the output clock, operable within the range of 10 to 133MHz.

Key Features

- Phase-Lock Loop Clock Distribution

- 10MHz to 133MHz operating frequency

- Distributes one clock input to one bank of five outputs

- Zero Input-Output Delay

- Output Skew < 250ps