Datasheet Summary

Micrel, Inc.

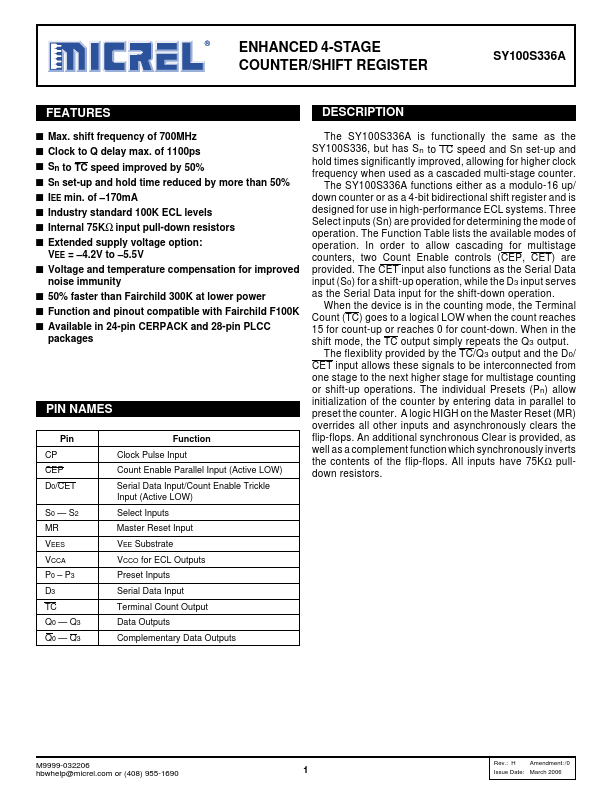

ENHANCED 4-STAGE COUNTER/SHIFT REGISTER

Features

DESCRIPTION s Max. shift frequency of 700MHz s Clock to Q delay max. of 1100ps s Sn to TC speed improved by 50% s Sn set-up and hold time reduced by more than 50% s IEE min. of

- 170mA s Industry standard 100K ECL levels s Internal 75KΩ input pull-down resistors s Extended supply voltage option:

VEE =

- 4.2V to

- 5.5V s Voltage and temperature pensation for improved noise immunity s 50% faster than Fairchild 300K at lower power s Function and pinout patible with Fairchild F100K s Available in 24-pin CERPACK and 28-pin PLCC packages

PIN NAMES

Pin CP CEP D0/CET

S0

- S2 MR VEES VCCA P0

- P3 D3 TC Q0

-...