SY100S331

SY100S331 is TRIPLE D FLIP-FLOP manufactured by Micrel Semiconductor.

Micrel, Inc.

NOT REMENDED FOR NEW DESIGNS

TRIPLE D FLIP-FLOP

Features

DESCRIPTION

- Max. toggle frequency of 800MHz

- Differential outputs

- IEE min. of

- 80m A

- Industry standard 100K ECL levels

- Extended supply voltage option:

VEE =

- 4.2V to

- 5.5V

- Voltage and temperature pensation for improved noise immunity

- Internal 75kΩ input pull-down resistors

- 150% faster than Fairchild

- 40% lower power than Fairchild

- Function and pinout patible with Fairchild F100K

- Available in 28-pin PLCC package

The SY100S331 offers three D-type, edge-triggered master/ slave flip-flops with true and plement outputs, designed for use in high-performance ECL systems. Each flip-flop is controlled by a mon clock (CPc), as well as its own clock pulse (CPn). The resultant clock signal controlling the flip-flop is the logical OR operation of these two clock signals. Data enters the master when both CPc and CPn are LOW and enters the slave on the rising edge of either CPc or CPn (or both).

Additional control signals include Master Set (MS) and Master Reset (MR) inputs. Each flip-flop also has its own Direct Set (SDn) and Direct Clear (CDn) signals. The MR, MS, SDn and DCn signals override the clock signals. The inputs on this device have 75kΩ pull-down resistors.

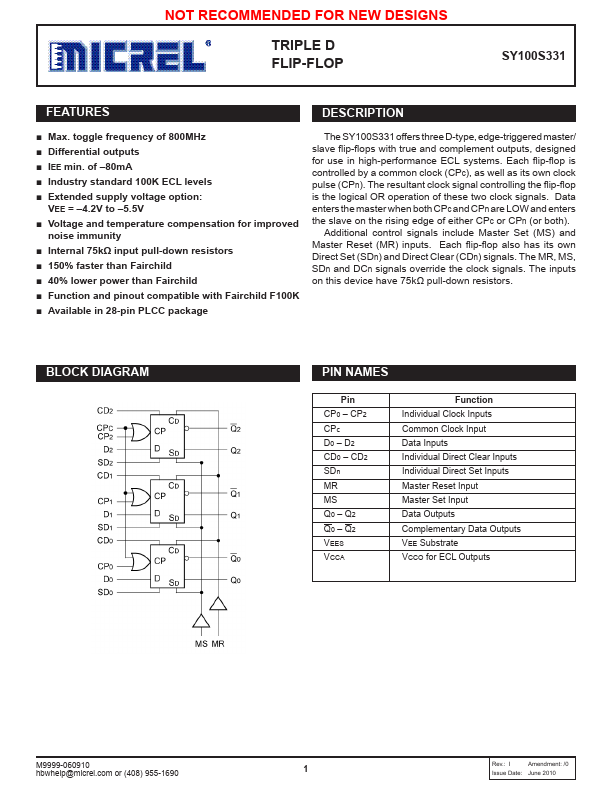

BLOCK DIAGRAM

PIN NAMES

Pin CP0

- CP2 CPc D0

- D2 CD0

- CD2 SDn MR MS Q0

- Q2 Q0

- Q2 VEES...