SSTUB32868 Key Features

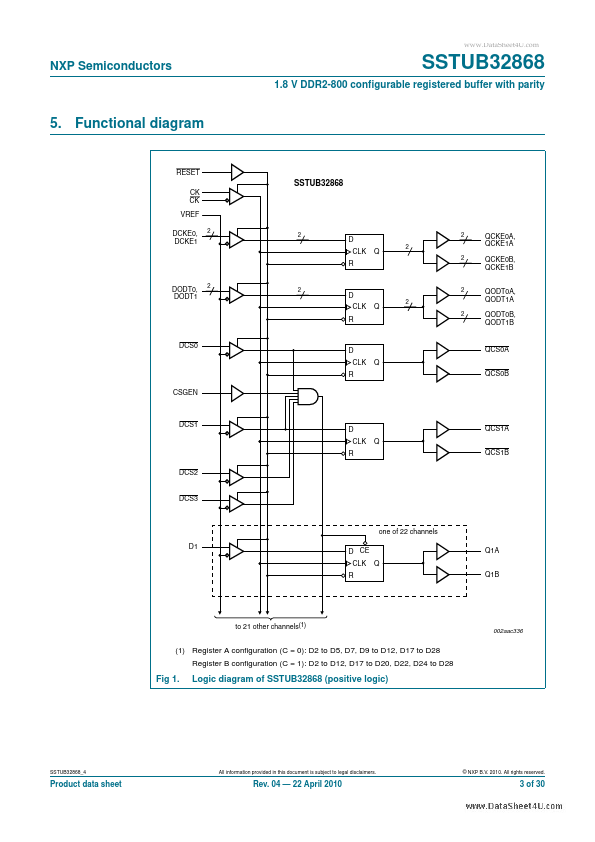

- 28-bit data register supporting DDR2

- Supports 2 rank by 4 DIMM density by integrating equivalent functionality of two JEDEC-standard DDR2 registers (that is,

- Parity checking function across 22 input data bits

- Parity out signal

- Controlled multi-impedance output impedance drivers enable optimal signal integrity and speed

- Meets or exceeds SSTUB32868 JEDEC standard speed performance

- Supports up to 450 MHz clock frequency of operation

- Programmable for normal or high output drive

- Optimized pinout for high-density DDR2 module design

- Chip-selects minimize power consumption by gating data outputs from changing state