PLL602-04

PLL602-04 is Low Phase Noise CMOS XO manufactured by PhaseLink.

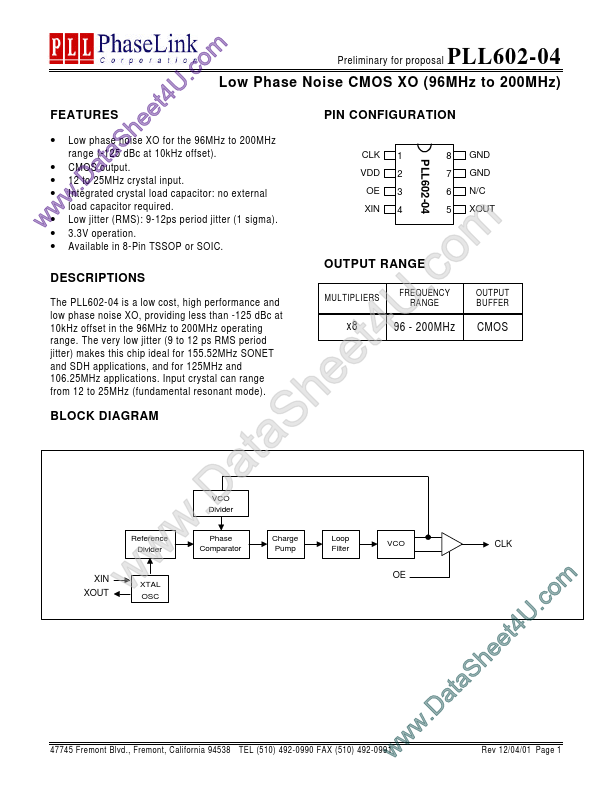

m Preliminary for proposal PLL602-04 o c . Low Phase Noise CMOS XO (96MHz to 200MHz) U t4 e Features

PIN CONFIGURATION e h XO for the 96MHz to 200MHz

- Low phase noise S range (-125 ta dBc at 10kHz offset).

- CMOS a output.

- 12 to .D25MHz crystal input.

- Integrated crystal load capacitor: no external w load capacitor required. w

- Low jitter (RMS): 9-12ps period jitter (1 sigma). w- 3.3V operation.

CLK 1 2 3 4 8 7 6 5 GND

VDD OE

N/C

- Available in 8-Pin TSSOP or SOIC.

DESCRIPTIONS

The PLL602-04 is a low cost, high performance and low phase noise XO, providing less than -125 dBc at 10kHz offset in the 96MHz to 200MHz operating range. The very low jitter (9 to 12 ps...