PLL650-06

PLL650-06 is Network LAN Clock manufactured by PhaseLink.

Features

- -

- -

- -

- - w- w w

Full CMOS output swing with 40-mA output drive capability. 25-mA output drive at TTL level. Advanced, low power, sub-micron CMOS processes. 25MHz fundamental crystal or clock input. One output fixed at 50MHz One selectable frequency output of 66.6 or 75MHz (with Double Drive Strength output). Zero PPM synthesis error in all clocks. Ideal for Network switches. 3.3V operation. Available in 8-Pin 150mil SOIC.

.D at h S a t e e

4U

. m o c

Network LAN Clock

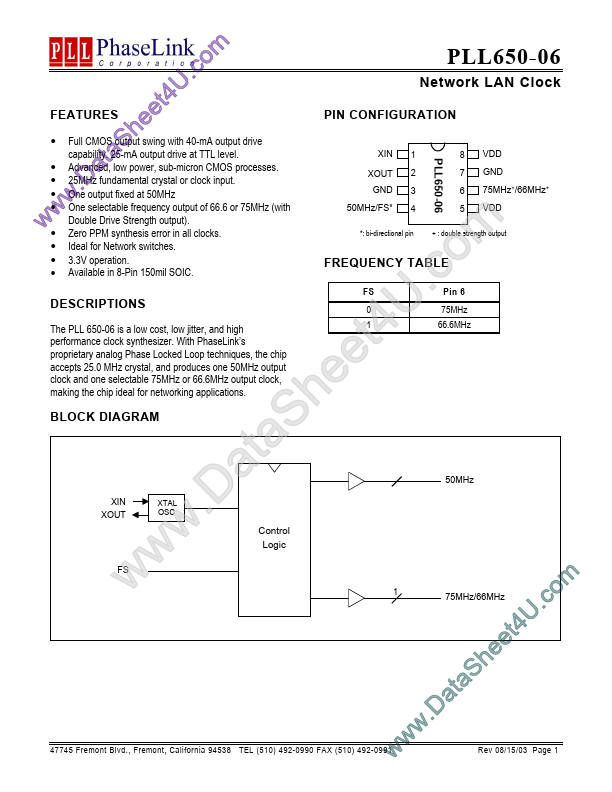

PIN CONFIGURATION

XIN XOUT GND 50MHz/FS- 1 2 3 4 8 7 6 5 VDD GND 75MHz+/66MHz+ VDD

- : bi-directional pin

+ : double strength output

FREQUENCY TABLE

DESCRIPTIONS

The PLL...