2308B Description

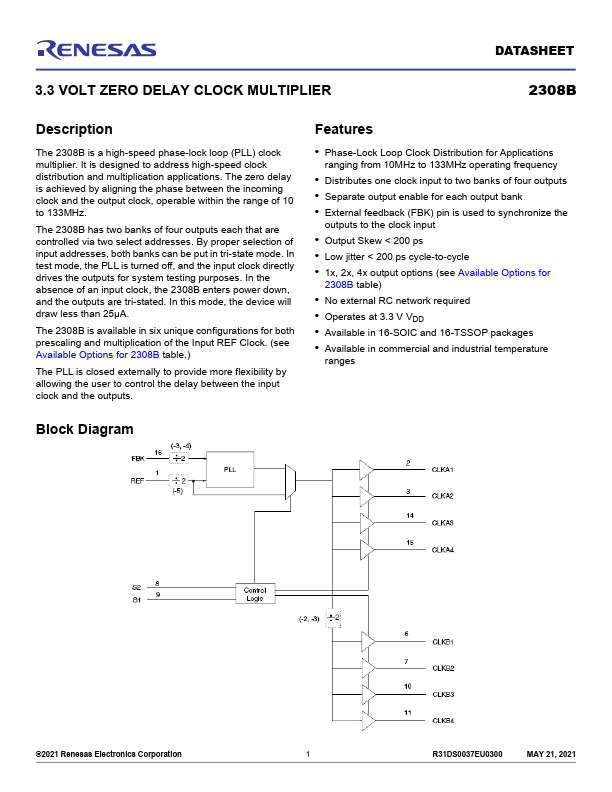

The 2308B is a high-speed phase-lock loop (PLL) clock multiplier. It is designed to address high-speed clock distribution and multiplication applications. The zero delay is achieved by aligning the phase between the ining clock and the output clock, operable within the range of 10 to 133MHz.

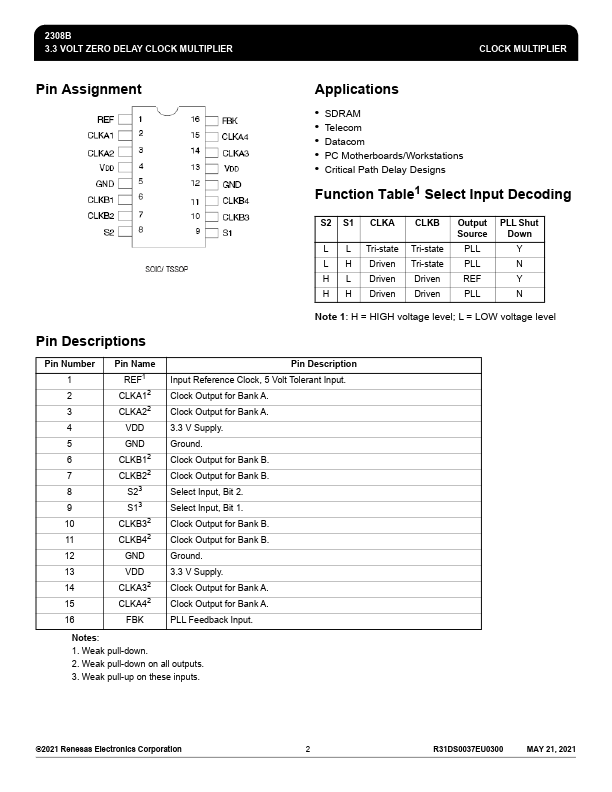

2308B Applications

- Phase-Lock Loop Clock Distribution for Applications

- Distributes one clock input to two banks of four outputs

- Separate output enable for each output bank

- External feedback (FBK) pin is used to synchronize the