SI53305

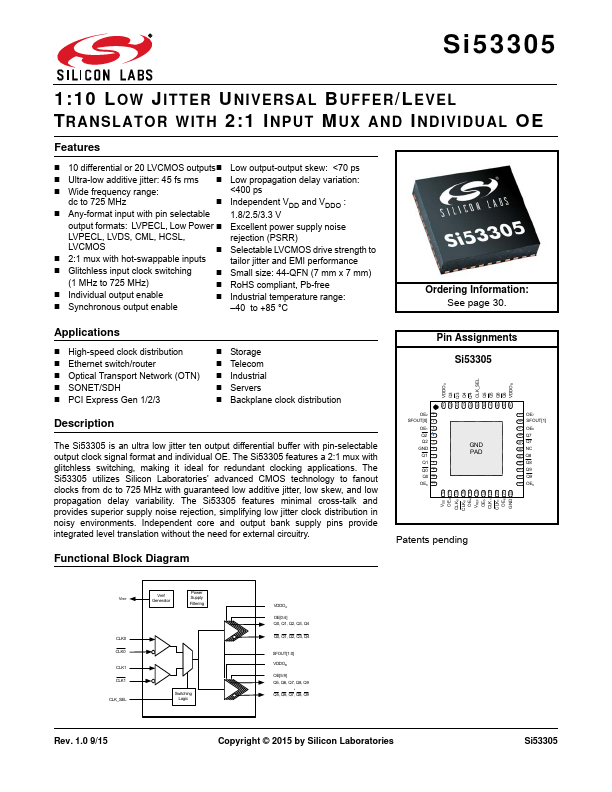

Description

The Si53305 is an ultra low jitter ten output differential buffer with pin-selectable output clock signal format and individual OE. The Si53305 features a 2:1 mux with glitchless switching, making it ideal for redundant clocking applications.

Key Features

- 10 differential or 20 LVCMOS outputs

- Low output-output skew: <70 ps

- Ultra-low additive jitter: 45 fs rms

- Low propagation delay variation

- Wide frequency range: <400 ps dc to 725 MHz

- Independent VDD and VDDO

- Any-format input with pin selectable 1.8/2.5/3.3 V output formats: LVPECL, Low Power

- Excellent power supply noise LVPECL, LVDS, CML, HCSL, rejection (PSRR) LVCMOS

- Selectable LVCMOS drive strength to

- 2:1 mux with hot-swappable inputs tailor jitter and EMI performance