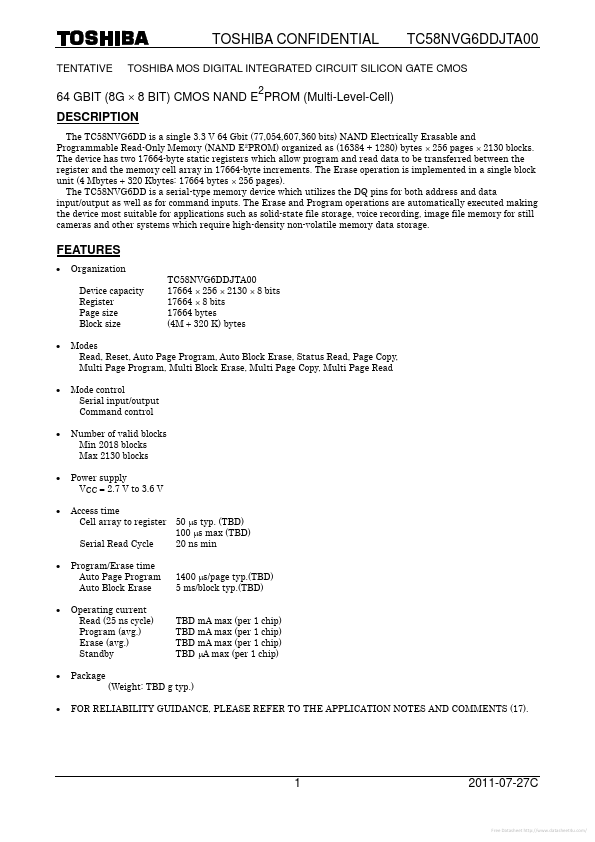

TC58NVG6DDJTA00

Overview

- Organization Device capacity Register Page size Block size

- TC58NVG6DDJTA00 17664 × 256 × 2130 × 8 bits 17664 × 8 bits 17664 bytes (4M + 320 K) bytes Modes Read, Reset, Auto Page Program, Auto Block Erase, Status Read, Page Copy, Multi Page Program, Multi Block Erase, Multi Page Copy, Multi Page Read Mode control Serial input/output Command control Number of valid blocks Min 2018 blocks Max 2130 blocks Power supply VCC = 2.7 V to 3.6 V Access time Cell array to register Serial Read Cycle 50 μs typ. (TBD) 100 μs max (TBD) 20 ns min 1400 μs/page typ.(TBD) 5 ms/block typ.(TBD) TBD mA max (per 1 chip) TBD mA max (per 1 chip) TBD mA max (per 1 chip) TBD μA max (per 1 chip) * * * *

- Program/Erase time Auto Page Program Auto Block Erase Operating current Read (25 ns cycle) Program (avg.) Erase (avg.) Standby Package * *

- (Weight: TBD g typ.) FOR RELIABILITY GUIDAN