WCSS0436V1P Key Features

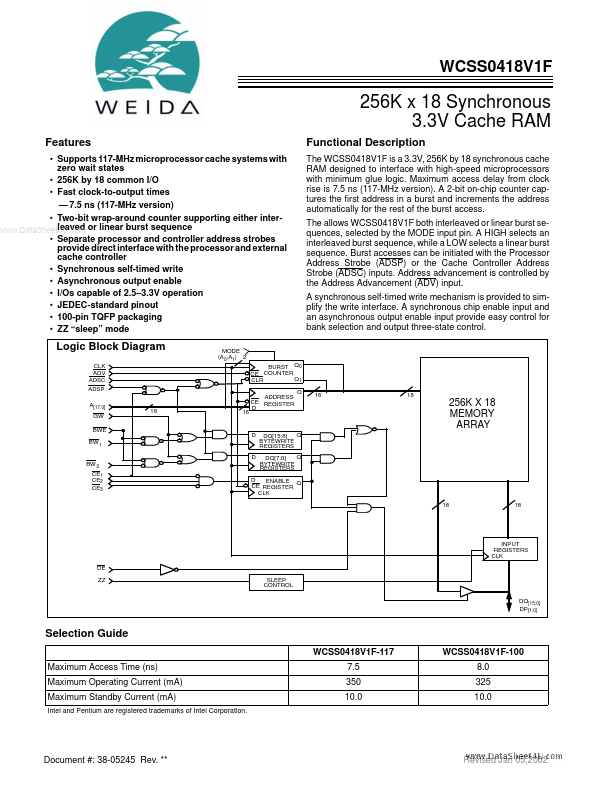

- Supports 117-MHz microprocessor cache systems with zero wait states

- 256K by 18 mon I/O

- Fast clock-to-output times

- 7.5 ns (117-MHz version)

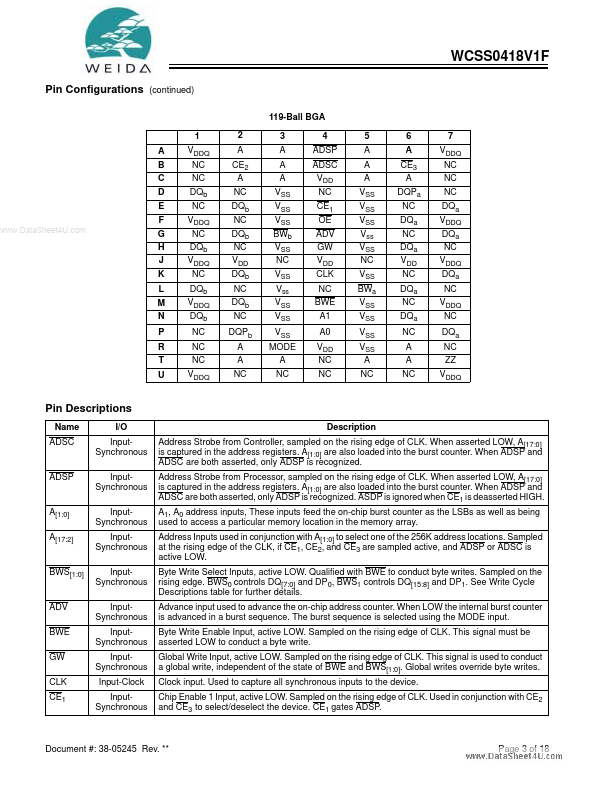

- Two-bit wrap-around counter supporting either interleaved or linear burst sequence

- Separate processor and controller address strobes provide direct interface with the processor and external cache control

- Synchronous self-timed write

- Asynchronous output enable

- I/Os capable of 2.5-3.3V operation

- JEDEC-standard pinout