CDCD5704

FEATURES

- High-Speed Clock Support: 300-MHz- 667-MHz Clock Source for XDR Memory Subsystems and Redwood Logic Interface

- Quad (Open-Drain) Differential Output Drivers

- Spread-Spectrum patible Clock Input Can

Be Distributed to Minimize EMI

- Differential or Single-Ended Reference Clock Input of 100 MHz or 133 MHz

- Serial Interface Features

: Programmable Frequency Multiplier, Select Any One to Four Outputs and Mode of Operation

- Supports Frequency Multiplication Factors of: ×3, ×4, ×5, ×6, ×8, ×9/2, ×15/2, ×15/4

- All PLL Loop Filter ponents Are Integrated

- Low |Cycle-to-Cycle| of 1- 6 Cycle Jitter:

- 40 ps: 300- 635 MHz

- 30 ps: 636- 667 MHz

- PLLs Are Powered Down if No Valid REF Clock (<10 MHz) Is Detected or VDD Is Below 1.6 V

- Operates From Single 2.5-V Supply (±0.125 V)

- Packaged in TSSOP-28

- mercial Temperature Range 0°C to 70°C

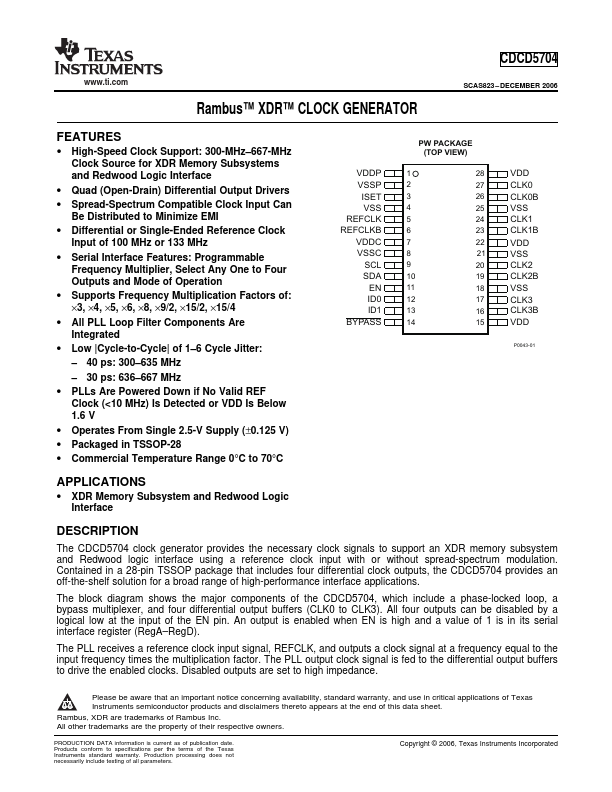

VDDP VSSP ISET

VSS REFCLK REFCLKB

VDDC VSSC

SCL SDA

EN ID0 ID1 BYPASS

PW PACKAGE (TOP VIEW)

1 28 2 27 3 26 4 25 5 24 6 23 7 22 8 21 9 20 10 19 11...