Description

Low Cost DSP Microcomputers ADSP-2104/ADSP-2109

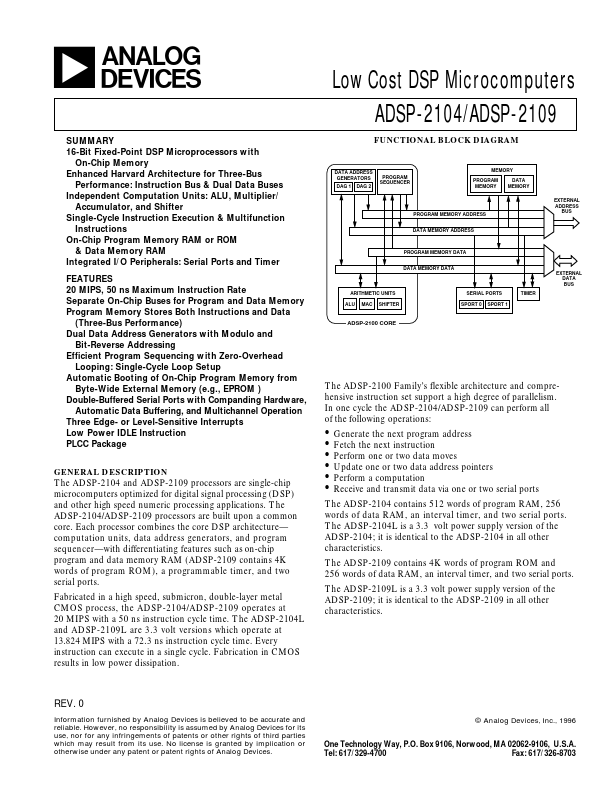

FUNCTIONAL BLOCK DIAGRAM

DATA ADDRESS GENERATORS DAG 1 DAG 2 MEMORY PROGRAM SEQUENCER PROGRAM MEMORY DATA MEMORY EXTERNAL ADDRESS BUS

PROGRAM MEMORY ADDRESS

DATA MEMORY ADDRESS

PROGRAM MEMORY DATA DATA MEMORY DATA EXTERNAL DATA BUS ARITHMETIC UNITS ALU MAC SHIFTER SERIAL PORTS SPORT 0 SPORT 1 TIMER

ADSP-2100 CORE

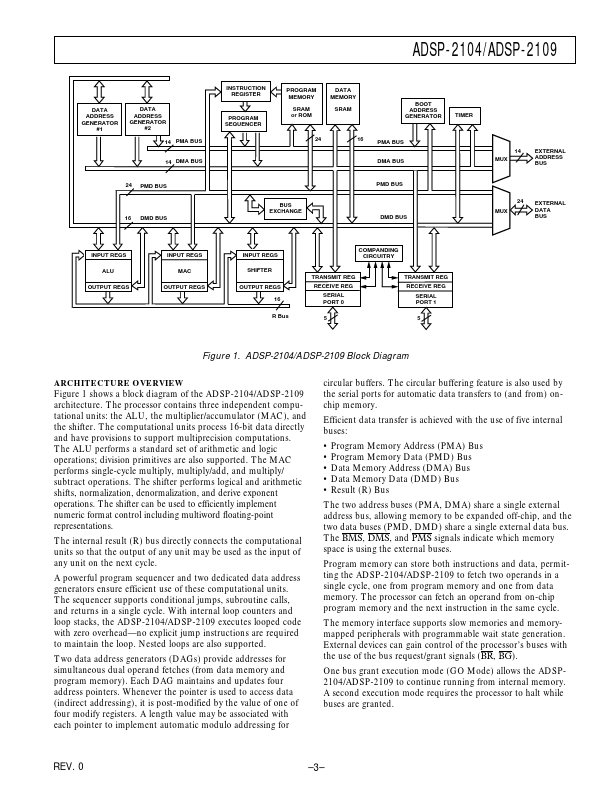

The ADSP-2100 Family’s flexible architecture and comprehensive instruction set support a high degree of parallelism.In one cycle t

Features

- 20 MIPS, 50 ns Maximum Instruction Rate Separate On-Chip Buses for Program and Data Memory Program Memory Stores Both Instructions and Data (Three-Bus Performance) Dual Data Address Generators with Modulo and Bit-Reverse Addressing Efficient Program Sequencing with Zero-Overhead Looping: Single-Cycle Loop Setup Automatic Booting of On-Chip Program Memory from Byte-Wide External Memory (e. g. , EPROM ) Double-Buffered Serial Ports with Companding Hardware, Automatic Data Buffering, and Multichannel.