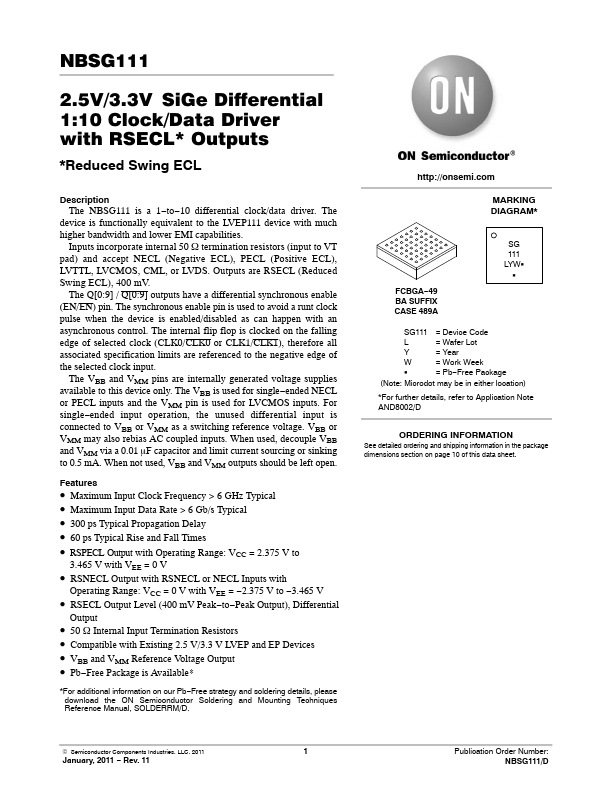

NBSG111

Overview

- Maximum Input Clock Frequency > 6 GHz Typical

- Maximum Input Data Rate > 6 Gb/s Typical

- 300 ps Typical Propagation Delay

- 60 ps Typical Rise and Fall Times

- RSPECL Output with Operating Range: VCC = 2.375 V to

- 465 V with VEE = 0 V

- RSNECL Output with RSNECL or NECL Inputs with Operating Range: VCC = 0 V with VEE = -2.375 V to -3.465 V

- RSECL Output Level (400 mV Peak-to-Peak Output), Differential Output

- 50 W Internal Input Termination Resistors

- Compatible with Existing 2.5 V/3.3 V LVEP and EP Dev