Description

The 512-Mbit Double-Data-Rate SDRAM is a high-speed CMOS, dynamic random-access memory containing 536,870,912 bits.

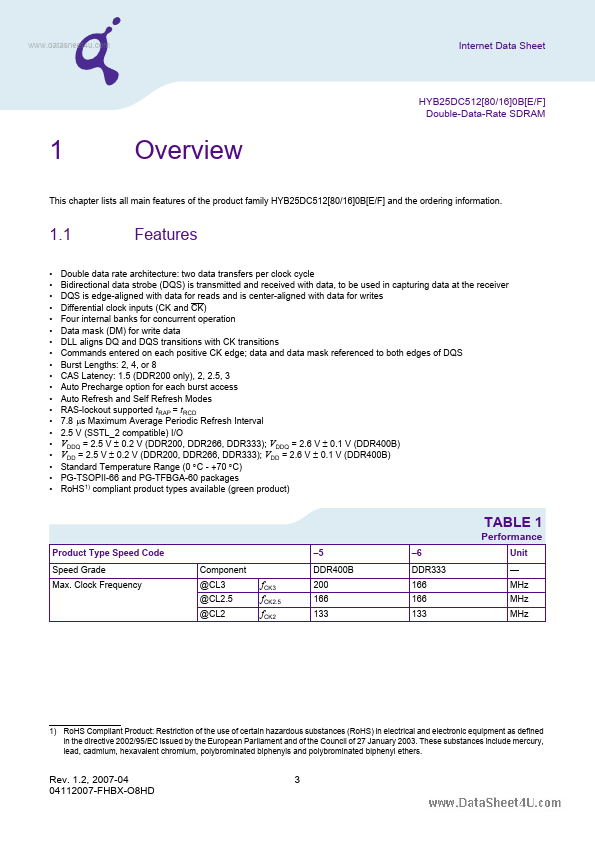

Features

- This chapter lists all main features of the product family HYB25DC512[80/16]0B[E/F] and the ordering information. Double data rate architecture: two data transfers per clock cycle Bidirectional data strobe (DQS) is transmitted and received with data, to be used in capturing data at the receiver DQS is edge-aligned with data for reads and is center-aligned with data for writes Differential clock inputs (CK and CK) Four internal banks for concurrent operation Data mask (DM) for write data DLL al.