Description

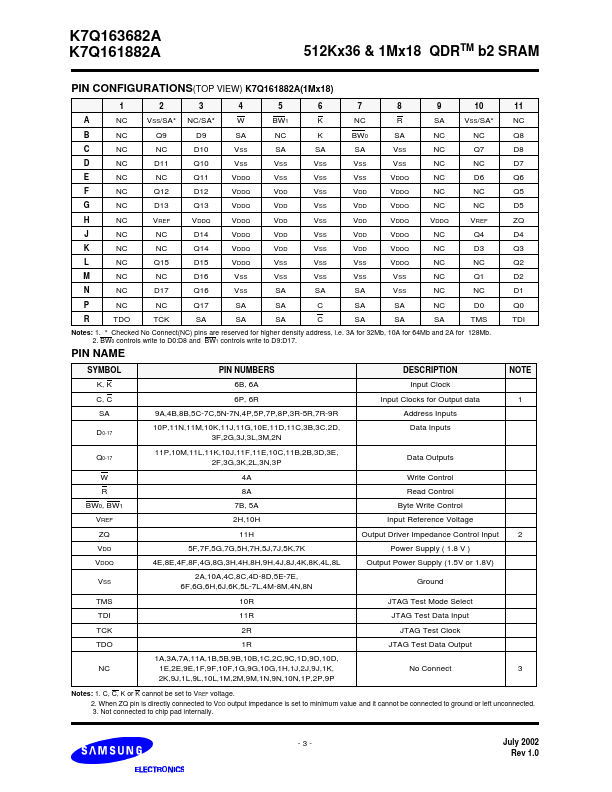

Input Clock Input Clocks for Output data Address Inputs Data Inputs 1 NOTE

Data Outputs Write Control Read Control Byte Write Control Input Reference Voltage Output Driver Impedance Control Input Power Supply ( 1.8 V ) Output Power Supply (1.5V or 1.8V) Ground JTAG Test Mode Select JTAG Test Data Input JTAG Test Clock JTAG Test Data Output No Connect 3 2

Notes: 1. C, C, K or K cannot be set to VREF voltage.2. When ZQ pin is directly connected to VDD output impedance is set to minimum value an

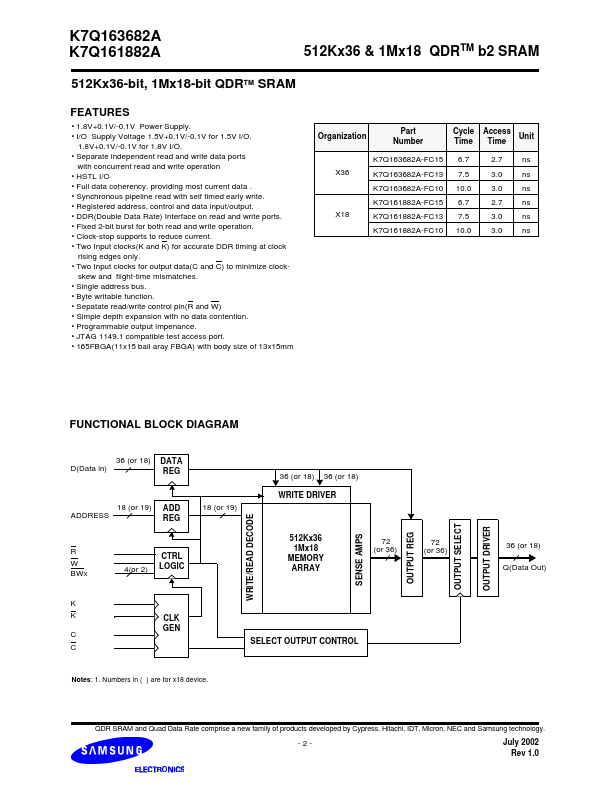

Features

- 1.8V+0.1V/-0.1V Power Supply.

- I/O Supply Voltage 1.5V+0.1V/-0.1V for 1.5V I/O, 1.8V+0.1V/-0.1V for 1.8V I/O.

- Separate independent read and write data ports with concurrent read and write operation.

- HSTL I/O.

- Full data coherency, providing most current data.

- Synchronous pipeline read with self timed early write.

- Registered address, control and data input/output.

- DDR(Double Data Rate) Interface on read and write ports.