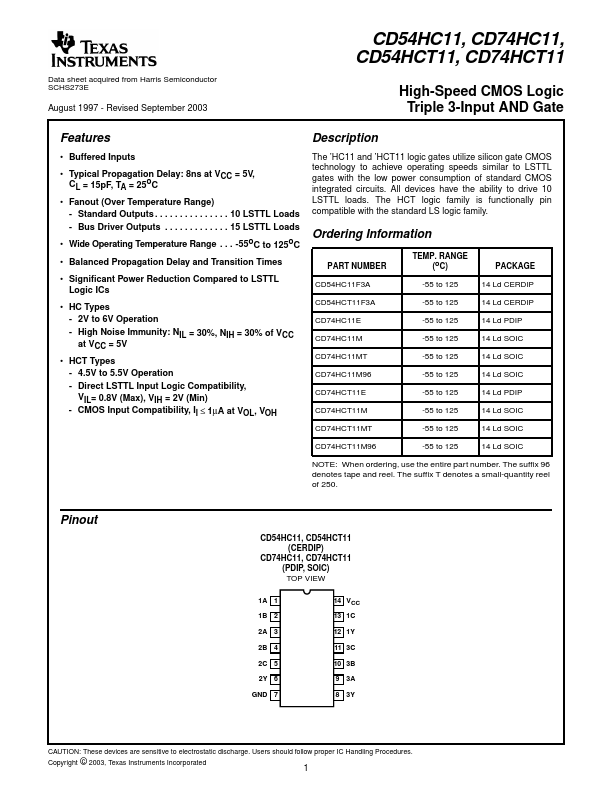

Datasheet Details

- Part number

- CD74HCT11, CD74HC11

- Manufacturer

- Texas Instruments ↗

- File Size

- 1.10 MB

- Datasheet

- CD74HC11-etcTI.pdf

- Description

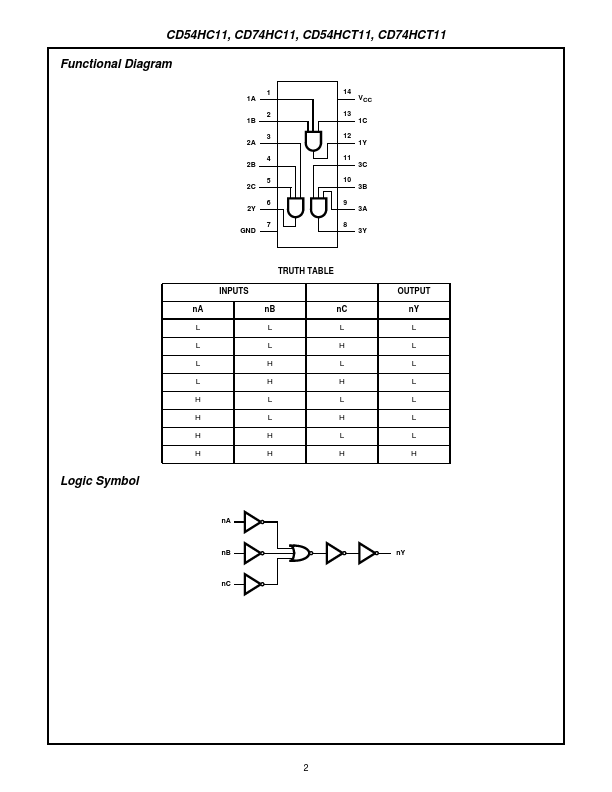

- High-Speed CMOS Logic Triple 3-Input AND Gate

- Note

- This datasheet PDF includes multiple part numbers: CD74HCT11, CD74HC11.

Please refer to the document for exact specifications by model.