AS4DDR32M16

AS4DDR32M16 is 8 Meg x 16 x 4 Banks Double Data Rate SDRAM COTS manufactured by Austin Semiconductor.

Austin Semiconductor, Inc. 8 Meg x 16 x 4 Banks

Double Data Rate SDRAM COTS, Plastic Encapsulated Microcircuit

Features

- VDD = +2.5V ±0.2V, VDDQ = +2.5V ±0.2V

- Bidirectional data strobe (DQS) transmitted/received with data, i.e., source-synchronous data capture (has two

- one per byte)

- Internal, pipelined double-data-rate (DDR) architecture; two data accesses per clock cycle

- Differential clock inputs (CK and CK#)

- mands entered on each positive CK edge

- DQS edge-aligned with data for READs; center-aligned with data for WRITEs

- DLL to align DQ and DQS transitions with CK

- Four internal banks for concurrent operation

- Data mask (DM) for masking write data (has two- one per byte)

- Programmable burst lengths: 2, 4, or 8

- Auto Refresh and Self Refresh Modes

- Longer lead TSOP for improved reliability (OCPL)

- 2.5V I/O (SSTL_2 patible)

- Concurrent auto precharge option is supported

- t RAS lockout supported (t RAP = t RCD)

CO TS PEM COTS SDRAM

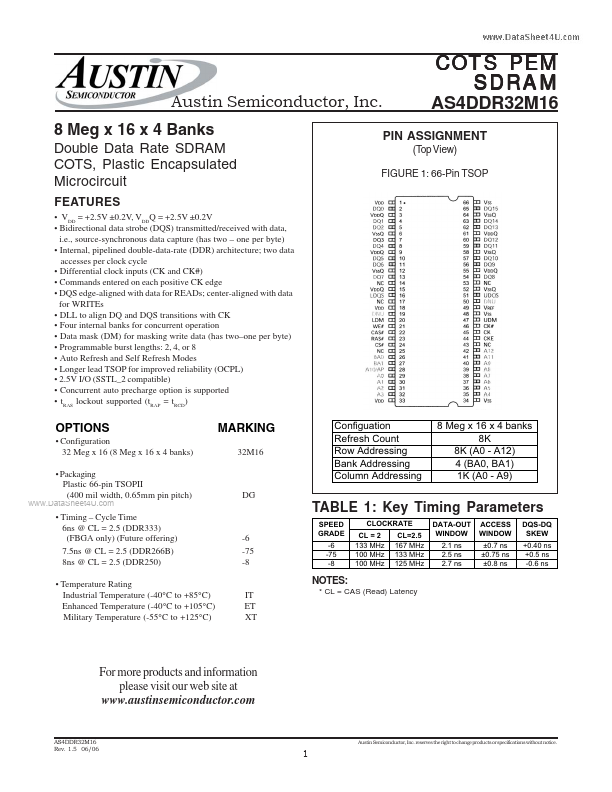

(Top View)

PIN ASSIGNMENT

FIGURE 1: 66-Pin TSOP

OPTIONS

- Configuration 32 Meg x 16 (8 Meg x 16 x 4 banks)

- Packaging Plastic 66-pin TSOPII (400 mil width, 0.65mm pin pitch)

..

MARKING

32M16

Configuation Refresh Count Row Addressing Bank Addressing Column...