AS4DDR32M72PBG

AS4DDR32M72PBG is 32Mx72 DDR SDRAM iNTEGRATED Plastic Encapsulated Microcircuit manufactured by Austin Semiconductor.

i PEM 2.4G b SDRAM-DDR 2.4Gb Austin Semiconductor, Inc. AS4DDR32M72PBG 32Mx72 DDR SDRAM i NTEGRATED Plastic Encapsulated Microcircuit

Features

- DDR SDRAM Data Rate = 200, 250, 266, 333Mbps

- Package:

BENEFITS

- 40% SPACE SAVINGS

- Reduced part count

- Reduced I/O count

- -

- -

- -

- -

- -

- -

- -

- -

- -

219 Plastic Ball Grid Array (PBGA), 32 x 25mm 2.5V ±0.2V core power supply 2.5V I/O (SSTL_2 patible) Differential clock inputs (CLK and CLK#) mands entered on each positive CLK edge Internal pipelined double-data-rate (DDR) architecture; two data accesses per clock cycle Programmable Burst length: 2,4 or 8 Bidirectional data strobe (DQS) transmitted/received with data, i.e., source-synchronous data capture (one per byte) DQS edge-aligned with data for READs; center-aligned with data for WRITEs DLL to align DQ and DQS transitions with CLK Four internal banks for concurrent operation Two data mask (DM) pins for masking write data Programmable IOL/IOH option Auto precharge option Auto Refresh and Self Refresh Modes Industrial, Enhanced and Military Temperature Ranges Organized as 32M x 72/80 Weight: AS4DDR32M72PBG </= 3.10 grams typical

- 34% I/O Reduction

- Reduced trace lengths for lower parasitic capacitance

- Suitable for hi-reliability applications

- Laminate interposer for optimum TCE match

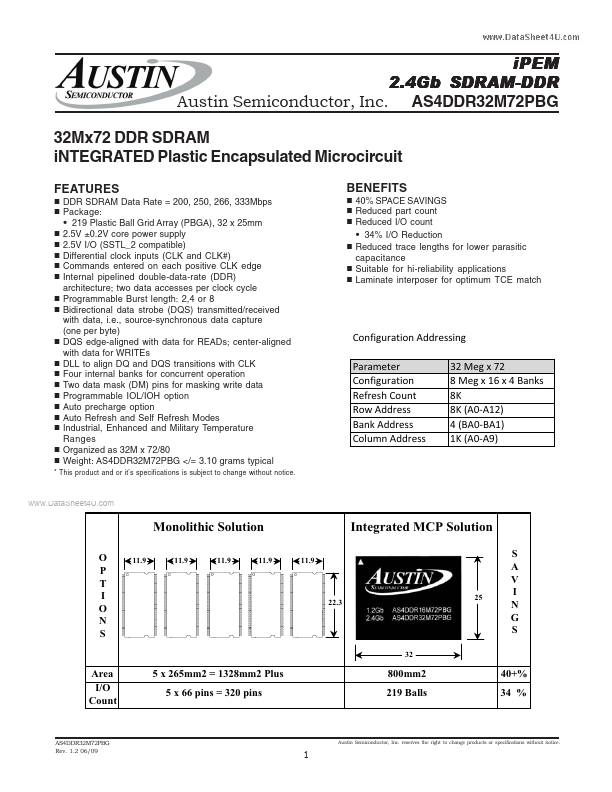

Configuration Addressing Parameter Configuration Refresh Count Row Address Bank Address Column Address 32Megx72 8Megx16x4Banks 8K 8K(A0ͲA12) 4(BA0ͲBA1) 1K(A0ͲA9)

- This product and or it’s specifications is subject to change without notice.

..

Monolithic Solution

O P T I O N S

11.9 11.9 11.9 11.9 11.9

Integrated MCP Solution

S A V I N G...