CY2DP1504

CY2DP1504 is 1:4 LVPECL Fanout Buffer manufactured by Cypress.

1:4 LVPECL Fanout Buffer with Selectable Clock Input

Features

- -

- -

- -

- -

- Functional Description

The CY2DP1504 is an ultra-low noise, low-skew, low-propagation delay 1:4 LVPECL fanout buffer targeted to meet the requirements of high-speed clock distribution applications. The CY2DP1504 can select between two separate LVPECL input clock pairs using the IN_SEL pin. The synchronous clock enable function ensures glitch-free output transitions during enable and disable periods. The device has a fully differential internal architecture that is optimized to achieve low additive jitter and low skew at operating frequencies of up to 1.5 GHz.

Select one of two low-voltage positive emitter-coupled logic (LVPECL) input pairs to distribute to four LVPECL output pairs 30 ps maximum output-to-output skew 480-ps maximum propagation delay 0.15-ps maximum additive RMS phase jitter at 156.25 MHz (12-k Hz to 20-MHz offset) Up to 1.5-GHz operation Synchronous clock enable function 20-pin thin shrunk small outline package (TSSOP) 2.5-V or 3.3-V operating voltage[1] mercial and industrial operating temperature range

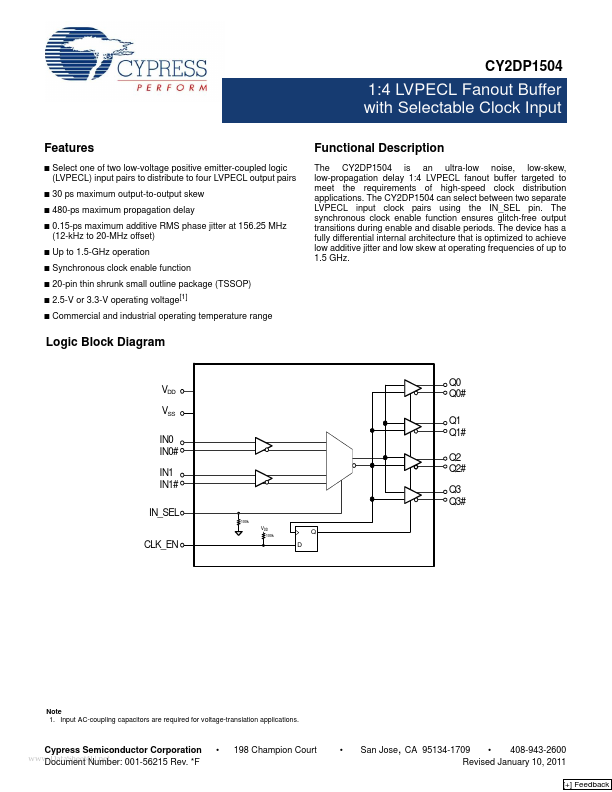

Logic Block Diagram

VDD VSS IN0 IN0# IN1 IN1# IN_SEL

100k

Q0 Q0# Q1 Q1# Q2 Q2# Q3 Q3#

100k

CLK_EN

Note 1. Input AC-coupling capacitors are required for voltage-translation applications.

..net

Cypress Semiconductor Corporation Document Number: 001-56215 Rev.

- F

- 198 Champion Court

- San Jose, CA 95134-1709

- 408-943-2600 Revised January 10, 2011

[+] Feedback

Contents

Pinouts .............................................................................. 3...