CY7C341B

CY7C341B is 192-Macrocell MAX EPLD manufactured by Cypress.

Features

- 192 macrocells in 12 logic array blocks (LABs)

- Eight dedicated inputs, 64 bidirectional I/O pins

- Advanced 0.65-micron CMOS technology to increase performance

- Programmable interconnect array

- 384 expander product terms

- Available in 84-pin HLCC, PLCC, and PGA packages macrocells within each LAB. Each LAB is interconnected with a programmable interconnect array, allowing all signals to be routed throughout the chip. The speed and density of the CY7C341B allows it to be used in a wide range of applications, from replacement of large amounts of 7400-series TTL logic, to plex controllers and multifunction chips. With greater than 37 times the functionality of 20-pin PLDs, the CY7C341B allows the replacement of over 75 TTL devices. By replacing large amounts of logic, the CY7C341B reduces board space, part count, and increases system reliability. Each LAB contains 16 macrocells. In LABs A, F, G, and L, 8 macrocells are connected to I/O pins and eight are buried, while for LABs B, C, D, E, H, I, J, and K, four macrocells are connected to I/O pins and 12 are buried. Moreover, in addition to the I/O and buried macrocells, there are 32 single product term logic expanders in each LAB. Their use greatly enhances the capability of the macrocells without increasing the number of product terms in each macrocell.

Functional Description

The CY7C341B is an Erasable Programmable Logic Device (EPLD) in which CMOS EPROM cells are used to configure logic functions within the device. The MAX® architecture is 100% user-configurable, allowing the devices to acmodate a variety of independent logic functions. The 192 macrocells in the CY7C341B are divided into 12 Logic Array Blocks (LABs), 16 per LAB. There are 384 expander product terms, 32 per LAB, to be used and shared by the

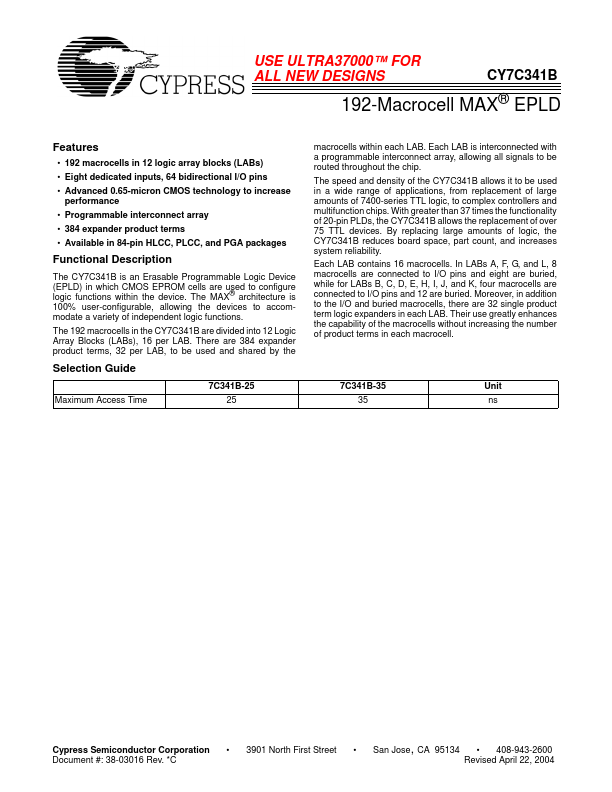

Selection Guide

7C341B-25 Maximum Access Time 25 7C341B-35 35 Unit ns

Cypress Semiconductor Corporation Document #: 38-03016 Rev.

- C

- 3901 North First Street

- San Jose, CA 95134

-...