CY7C342B Overview

Key Specifications

Package: DIP

Mount Type: Surface Mount, Through Hole

Pins: 68

Operating Voltage: 5 V

Key Features

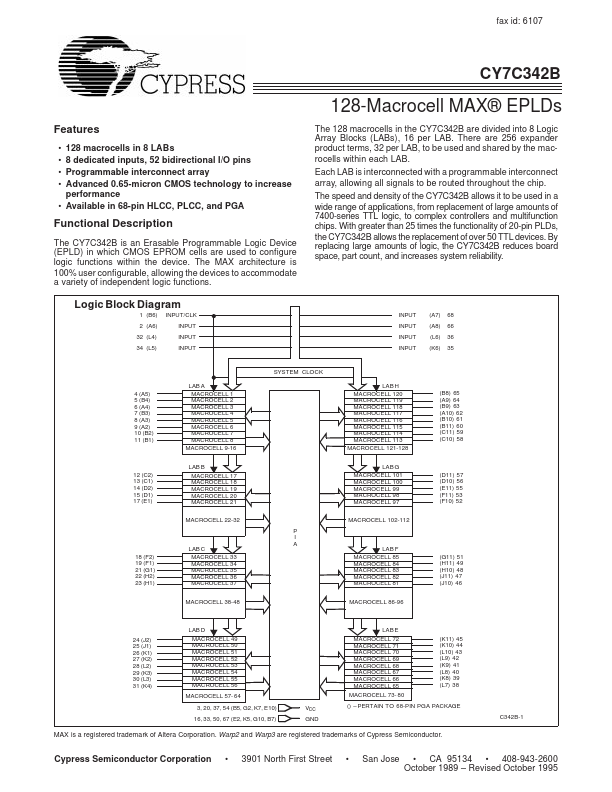

- 128 macrocells in 8 LABs

- 8 dedicated inputs, 52 bidirectional I/O pins

- Programmable interconnect array

- Advanced 0.65-micron CMOS technology to increase performance

- Available in 68-pin HLCC, PLCC, and PGA