CY7C1006D

Overview

- Pin- and function-compatible with CY7C106B/CY7C1006B

- High speed ❐ tAA = 10 ns

- Low active power ❐ ICC = 80 mA @ 10 ns

- Low CMOS standby power ❐ ISB2 = 3.0 mA

- 2.0 V Data Retention

- Automatic power-down when deselected

- CMOS for optimum speed/power

- TTL-compatible inputs and outputs

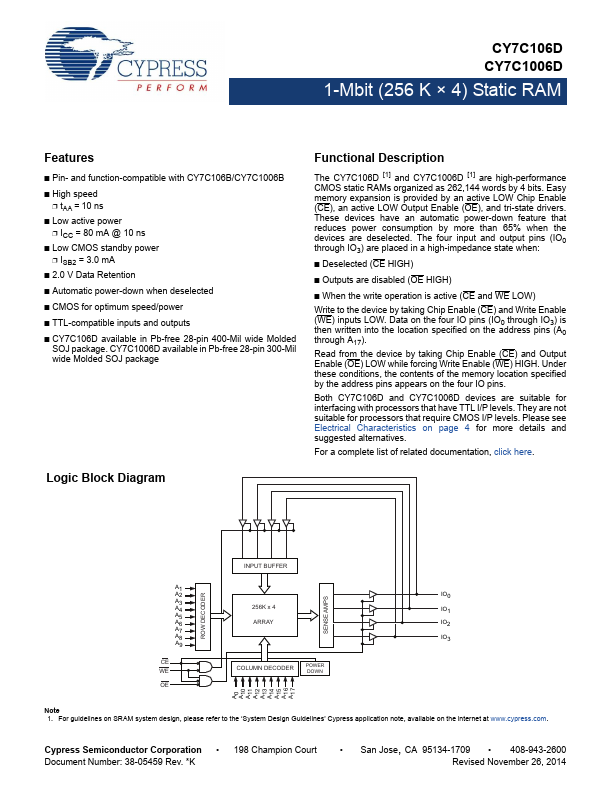

- CY7C106D available in Pb-free 28-pin 400-Mil wide Molded SOJ package. CY7C1006D available in Pb-free 28-pin 300-Mil wide Molded SOJ package Functional Description The CY7C106D [1] and CY7C1006D [1] are high-performance CMOS static RAMs organized as 262,144 words by 4 bits. Easy memory expansion is provided by an active LOW Chip Enable (CE), an active LOW Output Enable (OE), and tri-state drivers. These devices have an automatic power-down feature that reduces power consumption by more than 65% when the devices are deselected. The four input and output pins (IO0 through IO3) are plac