Datasheet Summary

PRELIMINARY DATA SHEET

MOS INTEGRATED CIRCUIT

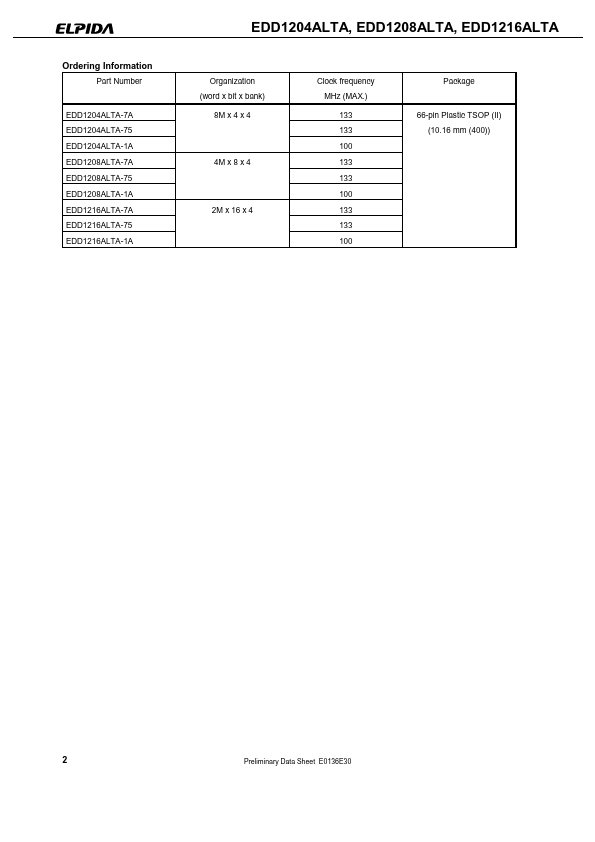

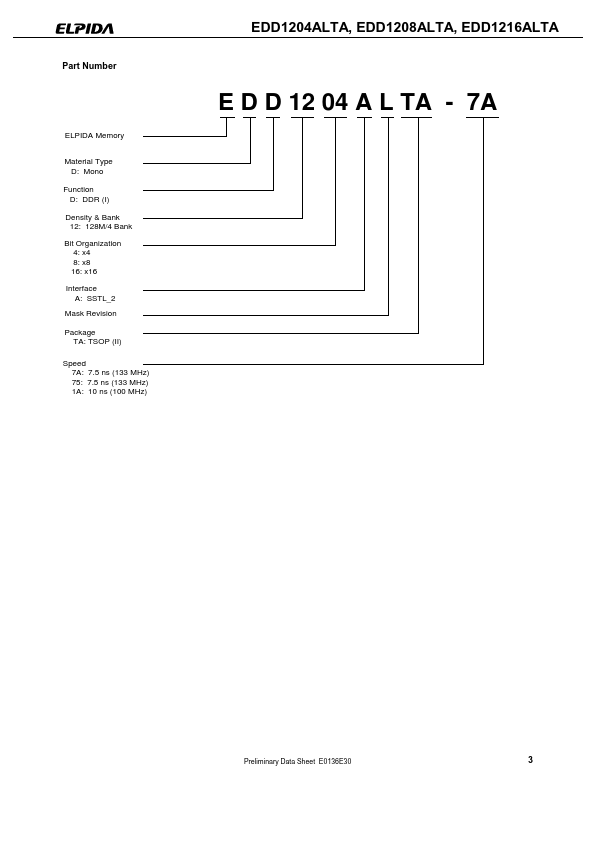

EDD1204ALTA, EDD1208ALTA, EDD1216ALTA

128 M-bit Synchronous DRAM with Double Data Rate (4-bank, SSTL_2)

Description The EDD1204ALTA, EDD1208ALTA, EDD1216ALTA are high-speed 134,217,728 bits synchronous dynamic random-access memories, organized as 8,388,608x4x4, 4,194,304x8x4, 2,097,152x16x4 (word x bit x bank), respectively.

The synchronous DRAMs use Double Data Rate (DDR) where data bandwidth is twice of regular synchronous DRAM.

The synchronous DRAM is patible with SSTL_2 (Stub Series terminated Logic for 2.5 V). The synchronous DRAM is packaged in 66-pin Plastic TSOP (II).

Features

- Fully Synchronous Dynamic RAM with all input signals...