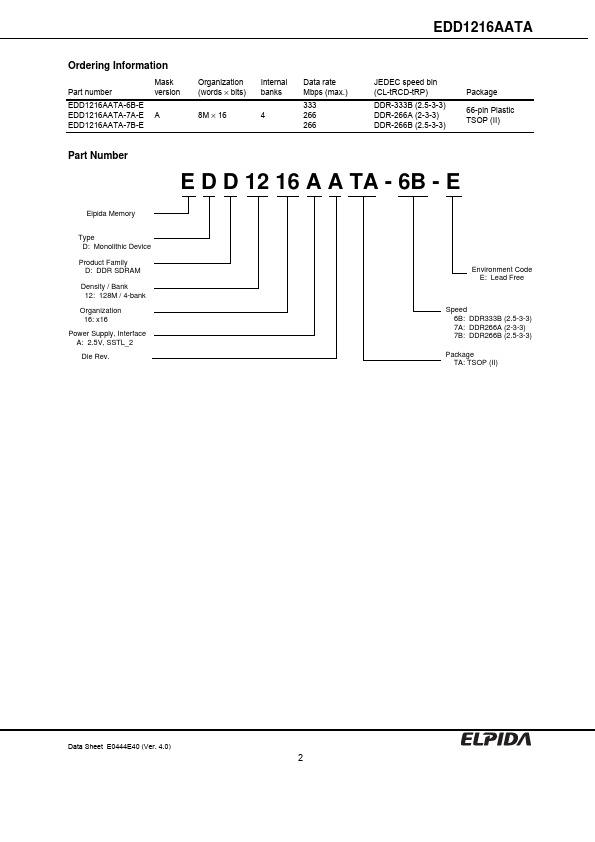

Datasheet Summary

DATA SHEET

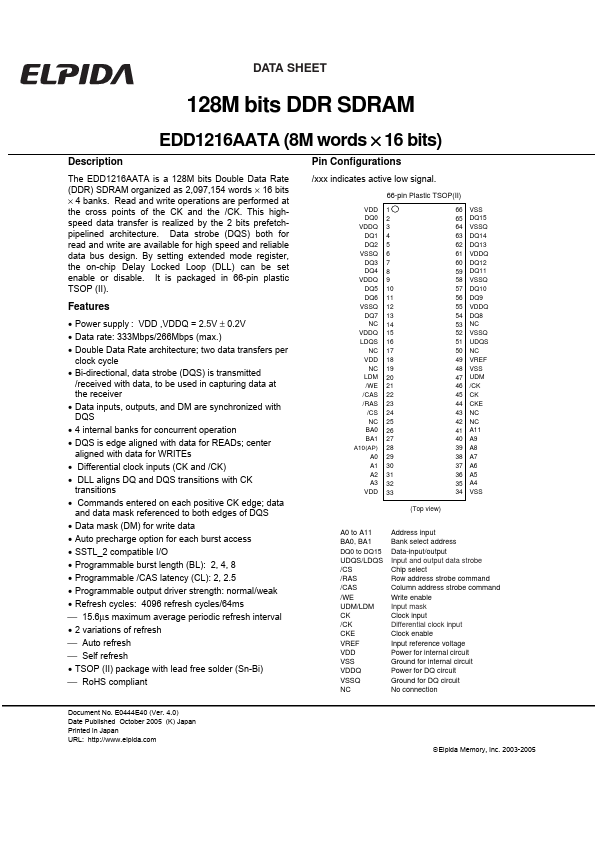

128M bits DDR SDRAM

EDD1216AATA (8M words × 16 bits)

Description

The EDD1216AATA is a 128M bits Double Data Rate (DDR) SDRAM organized as 2,097,154 words × 16 bits × 4 banks. Read and write operations are performed at the cross points of the CK and the /CK. This highspeed data transfer is realized by the 2 bits prefetchpipelined architecture. Data strobe (DQS) both for read and write are available for high speed and reliable data bus design. By setting extended mode register, the on-chip Delay Locked Loop (DLL) can be set enable or disable. It is packaged in 66-pin plastic TSOP (II).

Features

- Power supply : VDD ,VDDQ = 2.5V ± 0.2V

- Data rate: 333Mbps/266Mbps (max.)

-...