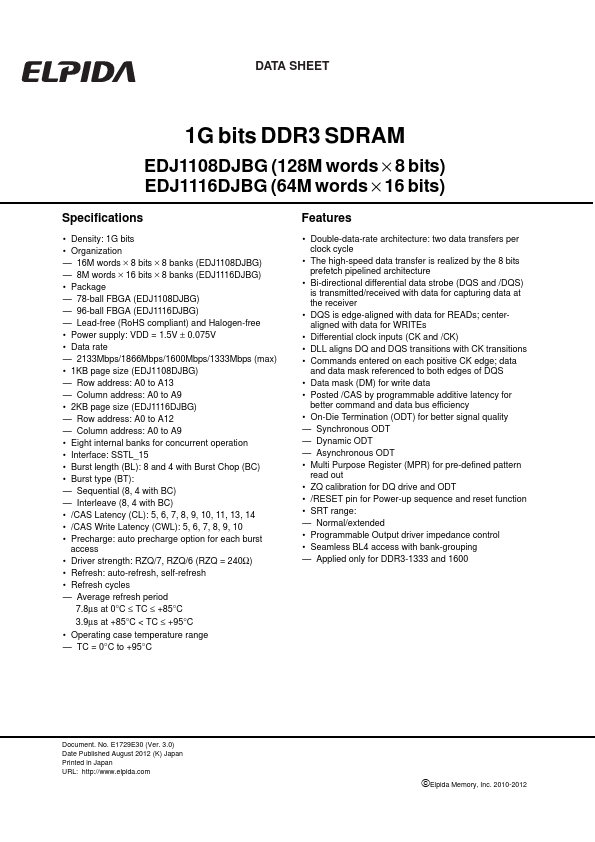

EDJ1108DJBG

EDJ1108DJBG is 1G bits DDR3 SDRAM manufactured by Elpida Memory.

Features

- Double-data-rate architecture: two data transfers per clock cycle

- The high-speed data transfer is realized by the 8 bits prefetch pipelined architecture

- Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the receiver

- DQS is edge-aligned with data for READs; centeraligned with data for WRITEs

- Differential clock inputs (CK and /CK)

- DLL aligns DQ and DQS transitions with CK transitions

- mands entered on each positive CK edge; data and data mask referenced to both edges of DQS

- Data mask (DM) for write data

- Posted /CAS by programmable additive latency for better mand and data bus efficiency

- On-Die Termination (ODT) for better signal quality

- Synchronous ODT

- Dynamic ODT

- Asynchronous ODT

- Multi Purpose Register (MPR) for pre-defined pattern read out

- ZQ calibration for DQ drive and ODT

- /RESET pin for Power-up sequence and reset function

- SRT range:

- Normal/extended

- Programmable Output driver impedance control

- Seamless BL4 access with bank-grouping

- Applied only for DDR3-1333 and 1600

Document. No. E1729E30 (Ver. 3.0) Date Published August 2012 (K) Japan Printed in Japan URL: http://.elpida.

©Elpida Memory, Inc. 2010-2012

EDJ1108DJBG, EDJ1116DJBG

Ordering Information

Part number EDJ1108DJBG-MU-F EDJ1108DJBG-JS-F EDJ1108DJBG-GN-F EDJ1108DJBG-DJ-F EDJ1116DJBG-MU-F EDJ1116DJBG-JS-F EDJ1116DJBG-GN-F EDJ1116DJBG-DJ-F Die revision Organization (words × bits) 128M × 8 Internal banks JEDEC speed bin (CL-t RCD-t RP) DDR3-2133L (14-14-14) DDR3-1866M (13-13-13) DDR3-1600K (11-11-11) DDR3-1333H (9-9-9) DDR3-2133L (14-14-14) DDR3-1866M (13-13-13) DDR3-1600K (11-11-11) DDR3-1333H (9-9-9) Package 78-ball FBGA

96-ball FBGA

64M × 16

Part Number

E D J 11 08 D J BG...