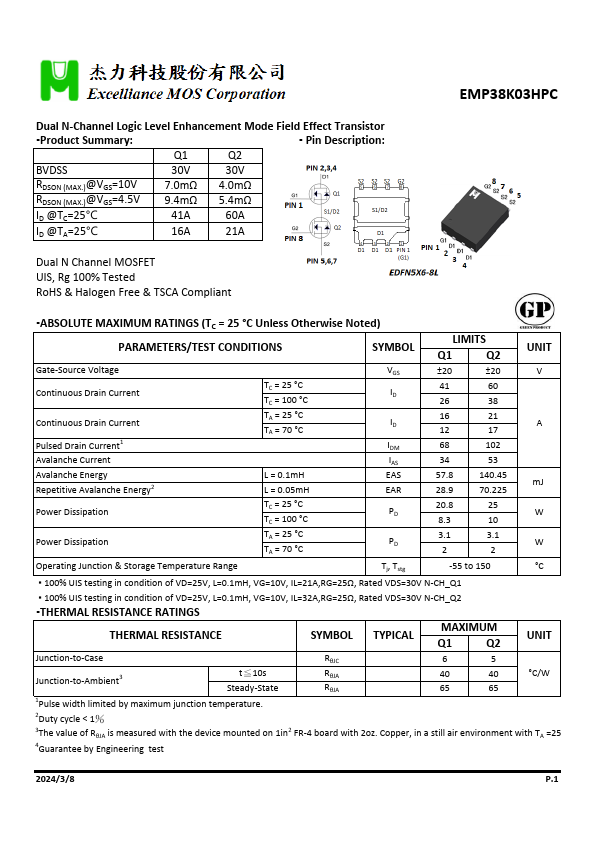

| Part | EMP38K03HPC |

|---|---|

| Description | Dual N-Channel Logic Level Enhancement Mode Field Effect Transistor |

| Category | Transistor |

| Manufacturer | Excelliance MOS |

| Size | 551.46 KB |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| BDT88 | Inchange Semiconductor | Silicon PNP Power Transistor |

| KD333 | Tesla Elektronicke | Transistor |

| C828 | SEMTECH | NPN Silicon Transistor |