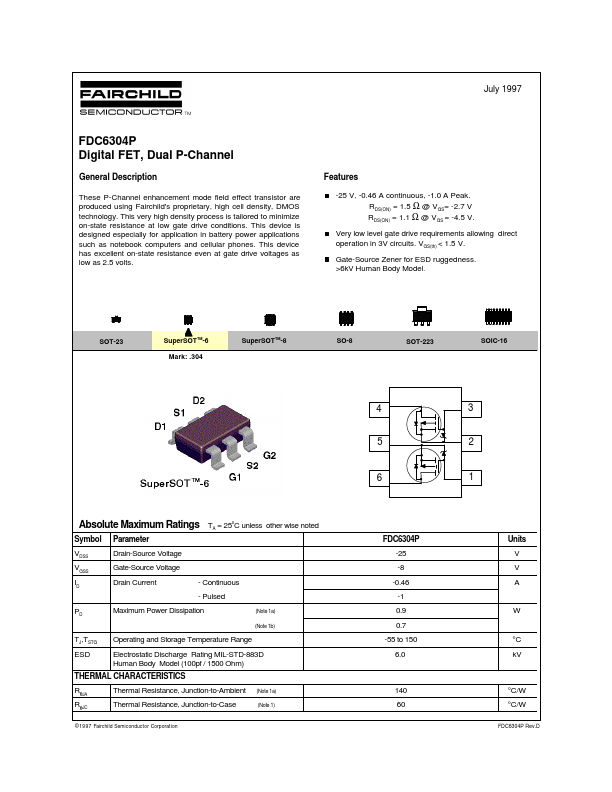

| Part | FDC6304P |

|---|---|

| Description | Digital FET/ Dual P-Channel |

| Manufacturer | Fairchild Semiconductor |

| Size | 74.28 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| FDC6304P | onsemi | Dual P-Channel MOSFET |

| FDC6301N | onsemi | Dual N-Channel Digital FET |

| FDC6302P | onsemi | Dual P-Channel MOSFET |

| FDC6305N | onsemi | Dual N-Channel MOSFET |

| FDC6306P | VBsemi | Dual P-Channel 20V MOSFET |