GTLP16T1655 Description

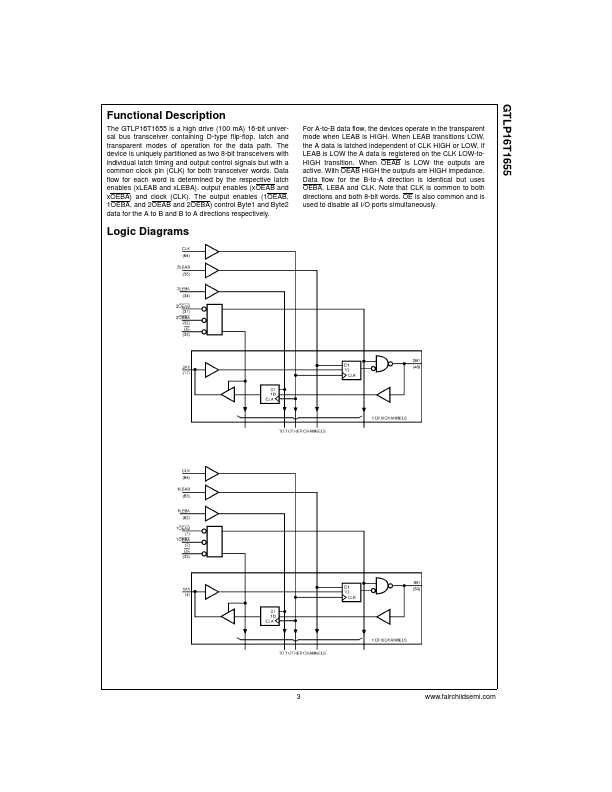

The GTLP16T1655 is a 16-bit universal bus transceiver that provides LVTTL to GTLP signal level translation. It allows for transparent, latched and clocked modes of data transfer. The device provides a high speed interface between cards operating at LVTTL logic levels and a backplane operating at GTLP logic levels.