LP750 Datasheet Text

0.5 W POWER PHEMT

- Features

- 28 dBm Output Power at 1-dB pression at 18 GHz

- 10 dB Power Gain at 18 GHz

- 24 dBm Output Power at 1-dB pression at 3.3V

- 55% Power-Added Efficiency

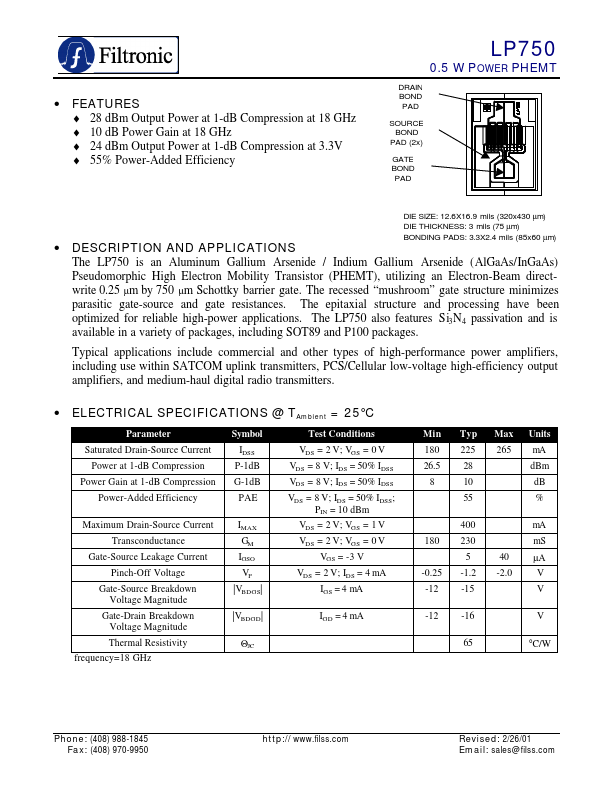

DRAIN BOND PAD SOURCE BOND PAD (2x) GATE BOND PAD

- DESCRIPTION AND APPLICATIONS The LP750 is an Aluminum Gallium Arsenide / Indium Gallium Arsenide (AlGaAs/InGaAs) Pseudomorphic High Electron Mobility Transistor (PHEMT), utilizing an Electron-Beam directwrite 0.25 µm by 750 µm Schottky barrier gate. The recessed “mushroom” gate structure minimizes parasitic gate-source and gate resistances. The epitaxial structure and processing have been optimized for reliable high-power applications. The LP750 also Features

Si3 N4 passivation and is available in a variety of packages, including SOT89 and P100 packages. Typical applications include mercial and other types of high-performance power amplifiers, including use within SAT uplink transmitters, PCS/Cellular low-voltage high-efficiency output amplifiers, and medium-haul digital radio transmitters.

DIE SIZE: 12.6X16.9 mils (320x430 µm) DIE THICKNESS: 3 mils (75 µm) BONDING PADS: 3.3X2.4 mils (85x60 µm)

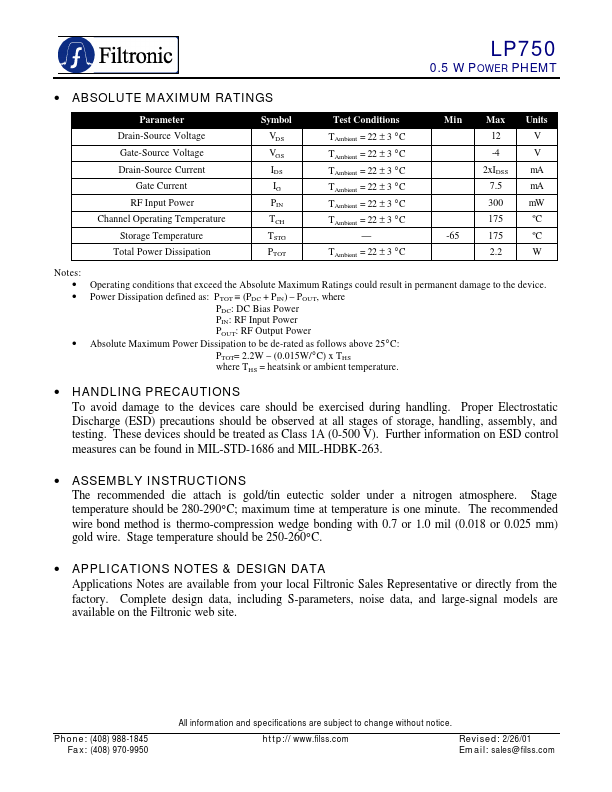

- ELECTRICAL SPECIFICATIONS @ TAmbient = 25 ° C

Parameter Saturated Drain-Source Current Power at 1-dB pression Power Gain at 1-dB pression Power-Added Efficiency Maximum Drain-Source Current Transconductance Gate-Source Leakage Current Pinch-Off Voltage Gate-Source Breakdown Voltage Magnitude Gate-Drain Breakdown Voltage Magnitude Thermal Resistivity frequency=18 GHz Symbol IDSS P-1dB G-1dB PAE IMAX GM IGSO VP |VBDGS| |VBDGD| ΘJC Test Conditions VDS = 2 V; VGS = 0 V VDS = 8 V; IDS = 50% IDSS VDS = 8 V; IDS = 50% IDSS VDS = 8 V; IDS = 50% IDSS; PIN = 10 dBm VDS = 2 V; VGS = 1 V VDS = 2 V; VGS = 0 V VGS = -3 V VDS = 2...