Datasheet Summary

128Mb Synchronous DRAM based on 2M x 4Bank x16 I/O Document Title

4Bank x 2M x 16bits Synchronous DRAM

Revision History

Revision No. 1.0 1.1 First Version Release 1. Corrected PIN ASSIGNMENT A12 to NC History Draft Date Dec. 2004 Jan. 2005 Remark

This document is a general product description and is subject to change without notice. Hynix does not assume any responsibility for use of circuits described. No patent licenses are implied. Rev. 1.1 / Jan. 2005 1

Synchronous DRAM Memory 128Mbit (8Mx16bit) HY57V281620E(L)T(P) Series

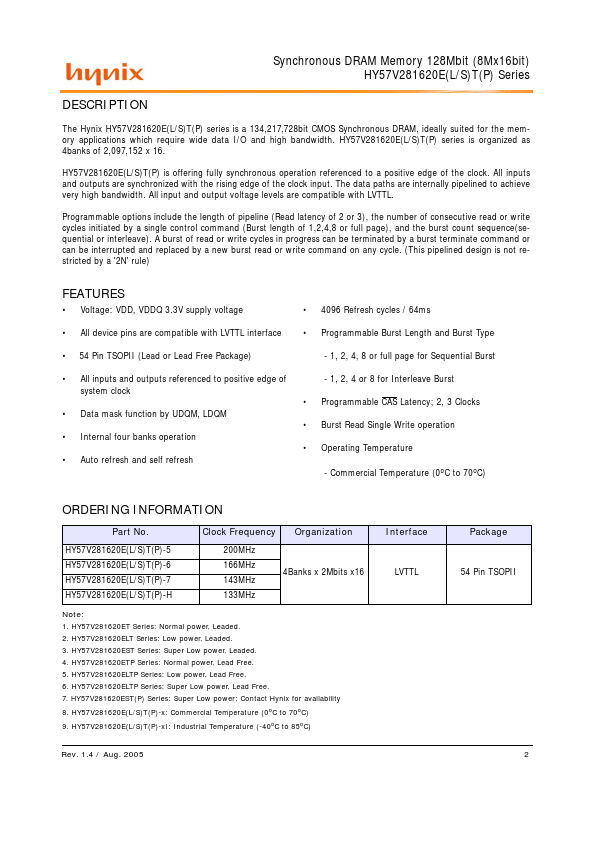

DESCRIPTION

The Hynix HY57V281620E(L)T(P) series is a 134,217,728bit CMOS Synchronous DRAM, ideally suited for the memory applications which require wide data I/O...