HY57V281620ETP Key Features

- Voltage: VDD, VDDQ 3.3V supply voltage

- 4096 Refresh cycles / 64ms

- All device pins are patible with LVTTL interface

- Programmable Burst Length and Burst Type

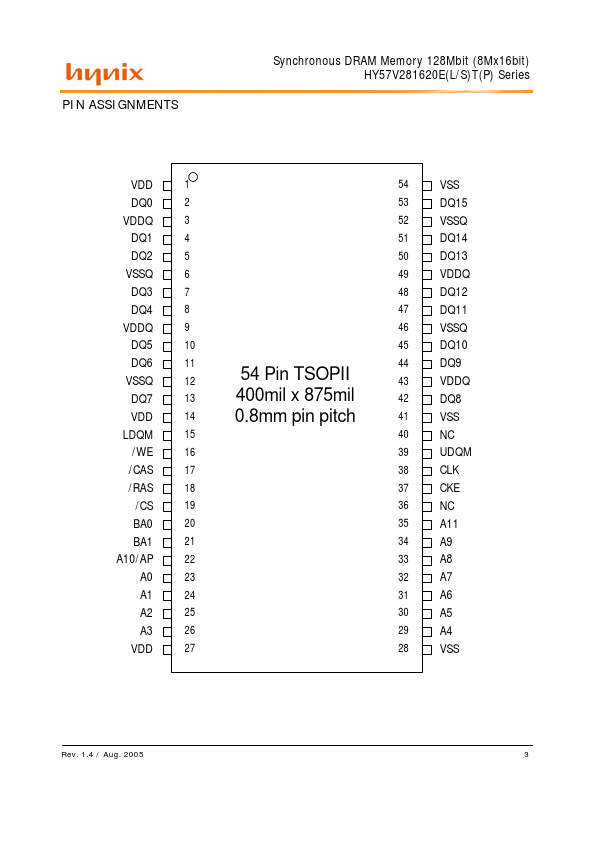

- 54 Pin TSOPII (Lead or Lead Free Package)

- 1, 2, 4, 8 or full page for Sequential Burst

- All inputs and outputs referenced to positive edge of system clock

- Data mask function by UDQM, LDQM

- Internal four banks operation

- Auto refresh and self refresh