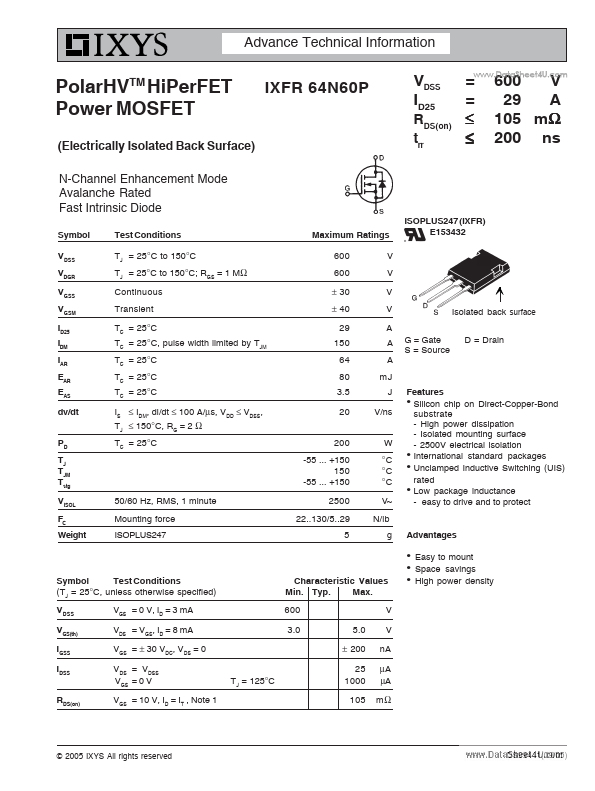

IXFR64N60P Description

+150 2500 22..130/5..29 5 V V V V A A A mJ J V/ns W °C °C °C V~ N/lb g RDS(on) trr = = ≤ ≤ .. 600 V 29 A 105 mΩ 200 ns ISOPLUS247 (IXFR) E153432 Isolated back surface G = Gate S = Source D = Drain.

IXFR64N60P Key Features

- High power dissipation

- Isolated mounting surface

- 2500V electrical isolation z International standard packages z Unclamped Inductive Switching (UIS) rated z Low package i

- easy to drive and to protect Advantages

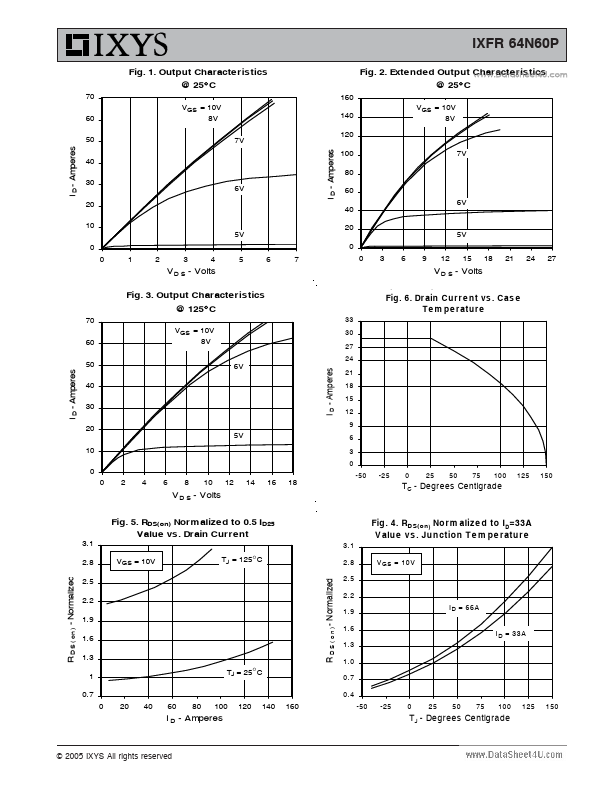

- Amperes

- Amperes