QS532807

QS532807 is GUARANTEED LOW SKEW CMOS CLOCK DRIVER/BUFFER manufactured by Integrated Device Technology.

QS532807 3.3V GUARANTEED LOW SKEW CMOS CLOCK DRIVER/BUFFER

INDUSTRIAL TEMPERATURE RANGE

GUARANTEED LOW SKEW CMOS CLOCK DRIVER/BUFFER

Features

:

- -

- -

- -

- JEDEC patible LVTTL level 10 low skew clock outputs Clock input is 5V tolerant Pinout and function patible with QS5807 25Ω on-chip resistors available for low noise Input hysteresis for better noise margin Guaranteed low skew:

- 0.35ns output skew (same bank)

- 0.6ns output skew (different bank)

- 0.75ns part-to-part skew Available in QSOP and SOIC packages

DESCRIPTION:

The QS532807 clock driver/buffer circuit can be used for clock buffering schemes where low skew is a key parameter. The QS532807 offers ten non-inverting outputs. Designed in IDT's proprietary QCMOS process, these devices provide low propagation delay buffering with onchip skew of 0.35ns for same-transition, same bank signals. The QS532807 has on-chip series termination resistors for lower noise clock signals. The QS532807 series resistor version is remended for driving unterminated lines with capacitive loading and other noise sensitive clock distribution circuits. These clock buffer products are designed for use in high-performance workstations, embedded and personal puting systems. Several devices can be used in parallel or scattered throughout a system for guaranteed low skew, system-wide clock distribution networks.

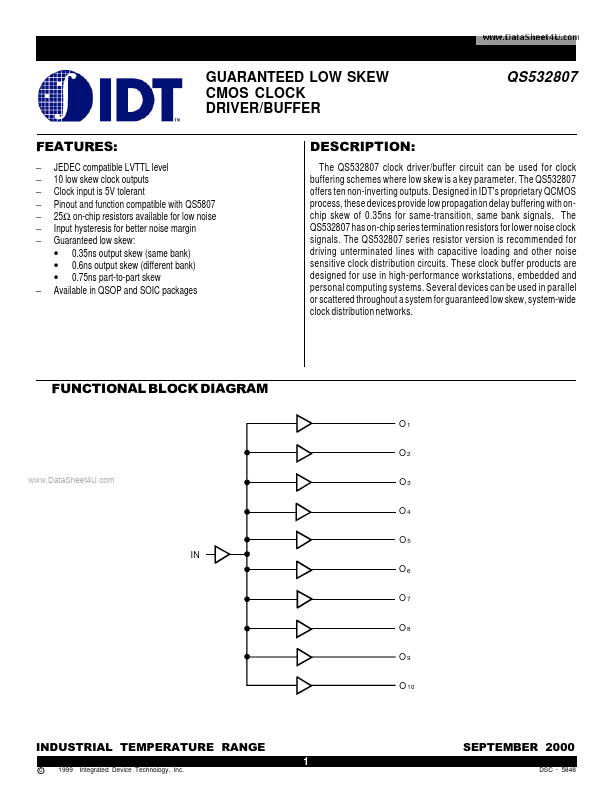

- FUNCTIONAL BLOCK DIAGRAM

O1 O2

..

O3 O4 O5 IN O6 O7 O8 O9 O 10

INDUSTRIAL TEMPERATURE RANGE

1 c 1999 Integrated Device Technology, Inc.

SEPTEMBER 2000

- 5848

QS532807 3.3V GUARANTEED LOW SKEW CMOS CLOCK DRIVER/BUFFER

INDUSTRIAL TEMPERATURE RANGE

PIN CONFIGURATION

IN G ND O1 V CC O2 G ND O3 V CC O4 G ND 1 2 3 4 5 6 7 8 9 10 20 19 18 17 SO 20-2 16 SO 20-8 15 14 13 12 11 VCC O 10 O9 G ND O8 VCC O7 G ND O6...