QS5930T

QS5930T is LOW SKEW CMOS PLL CLOCK DRIVER manufactured by Integrated Device Technology.

.Data Sheet.co.kr

QS5930T LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

INDUSTRIAL TEMPERATURE RANGE

LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

Features

:

- -

- -

- -

- -

- -

- -

- 5V operation Q/2 output, 5 Q outputs Useful for Pentium, Power PC, and PCI systems Internal loop filter RC network Low noise TTL level outputs <250ps rising edge output skew Balanced drive outputs ±24m A PLL bypass feature for low frequency testing Internal VCO/2 option for wider frequency range Outputs tri-state and reset while OE/RST is low ESD > 2000V Latch up > -300m A Available in QSOP package

DESCRIPTION

The QS5930T Clock Driver uses an internal phase locked loop (PLL) to lock low skew outputs to a reference clock input. Six outputs are available: Q0- Q4, Q/2. Careful layout and design ensure < 250ps skew between the Q0- Q4, and Q/2 outputs. The QS5930T includes an internal RC filter which provides excellent jitter characteristics and eliminates the need for external ponents. Various binations of feedback and a divide-by-2 in the VCO path allow applications to be customized for linear VCO operation over a wide range of input SYNC frequencies. The PLL can also be disabled by the PLL_EN signal to allow low frequency or DC testing. The QS5930T is designed for use in cost sensitive high-performance puting systems, workstations, multi-board puters, networking hardware, and mainframe systems. Several can be used in parallel or scattered throughout a system for guaranteed low skew, system-wide clock distribution networks. In the QSOP package, the QS5930T clock driver represents the best value in small form factor, high-performance clock management products. For more information on PLL clock driver products, see Application Note AN-227.

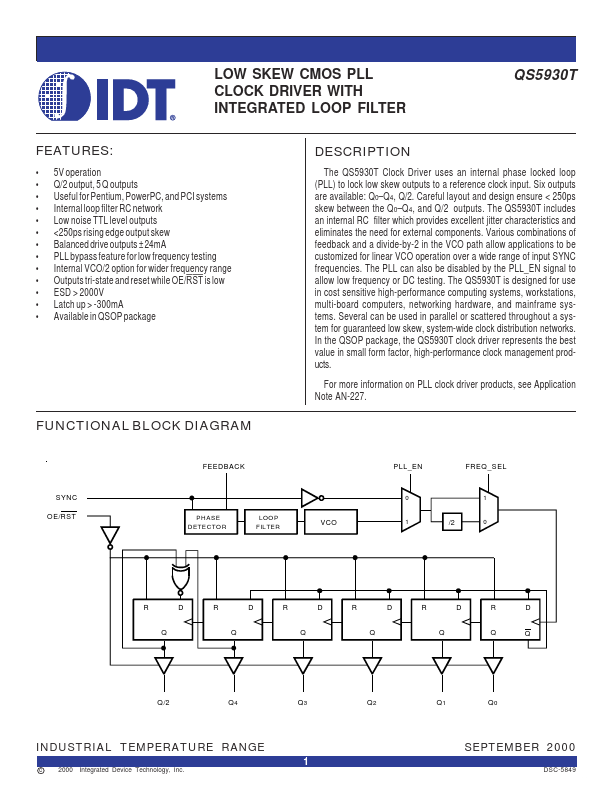

FUNCTIONAL BLOCK DIAGRAM

FEEDBACK PLL_EN FREQ _SEL

SYNC O E/RST

PH ASE DETECTO R LOO P FILTER

/2

Q /2

Q4

Q3

Q2

Q1

Q0

INDUSTR...