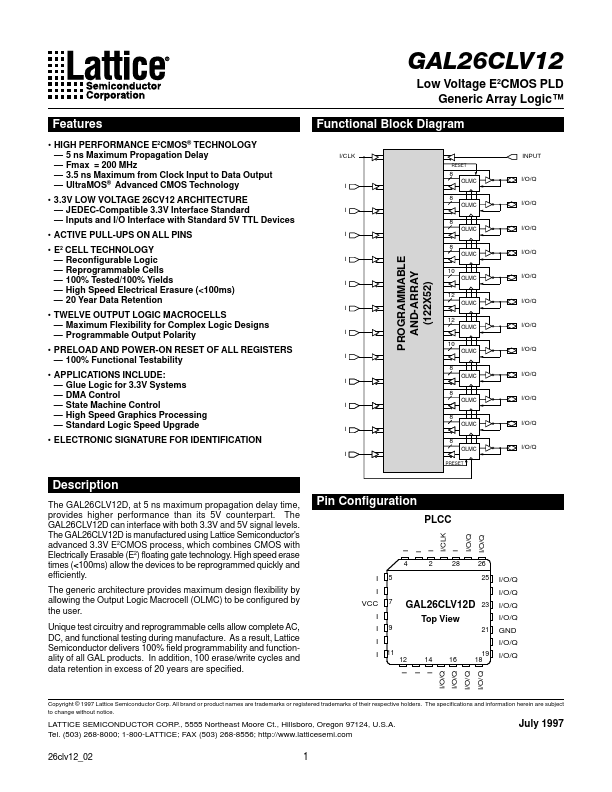

GAL26CLV12

GAL26CLV12 is Low Voltage E2CMOS PLD Generic Array Logic manufactured by Lattice Semiconductor.

Low Voltage E2CMOS PLD Generic Array Logic™

Features

Features

- HIGH PERFORMANCE E2CMOS® TECHNOLOGY

- 5 ns Maximum Propagation Delay

- Fmax = 200 MHz

- 3.5 ns Maximum from Clock Input to Data Output

- UltraMOS® Advanced CMOS Technology

- 3.3V LOW VOLTAGE 26CV12 ARCHITECTURE

- JEDEC-patible 3.3V Interface Standard

- Inputs and I/O Interface with Standard 5V TTL Devices

- ACTIVE PULL-UPS ON ALL PINS

- E2 CELL TECHNOLOGY

- Reconfigurable Logic

- Reprogrammable Cells

- 100% Tested/100% Yields

- High Speed Electrical Erasure (<100ms)

- 20 Year Data Retention

- TWELVE OUTPUT LOGIC MACROCELLS

- Maximum Flexibility for plex Logic Designs

- Programmable Output Polarity

- PRELOAD...